Other Parts Discussed in Thread: DS92LV18, DS25BR120

The DS25BR110 is being used to equalize/buffer a LVDS serdes signal after traveling over several meters of CAT5e cabling and output feeds into deserializer.

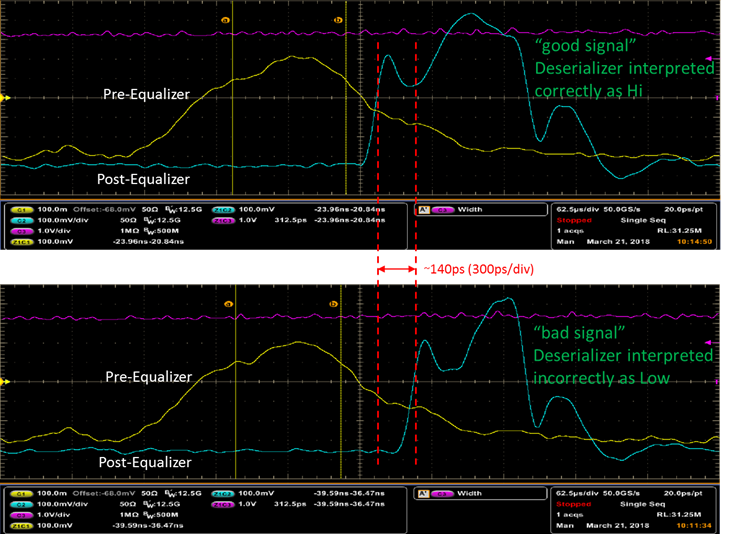

The following scope captures shows the serialized data coming into and output the DS25BR110. The scope is synchronized to RCLK of the deserializer. Note that the input signals look similar, yet the output of the "bad" output has a 140 ps delay on the front edge. End of pulse timing is the same This seems to be a binary occurrence, either it is correct or the pulse shortened by 140 ps.

What would cause this discrete shift?. The assumption is the equalizer operates as an analog filter, followed by an LVDS driver to restore the LVDS signal level and edge speed.