Hello,

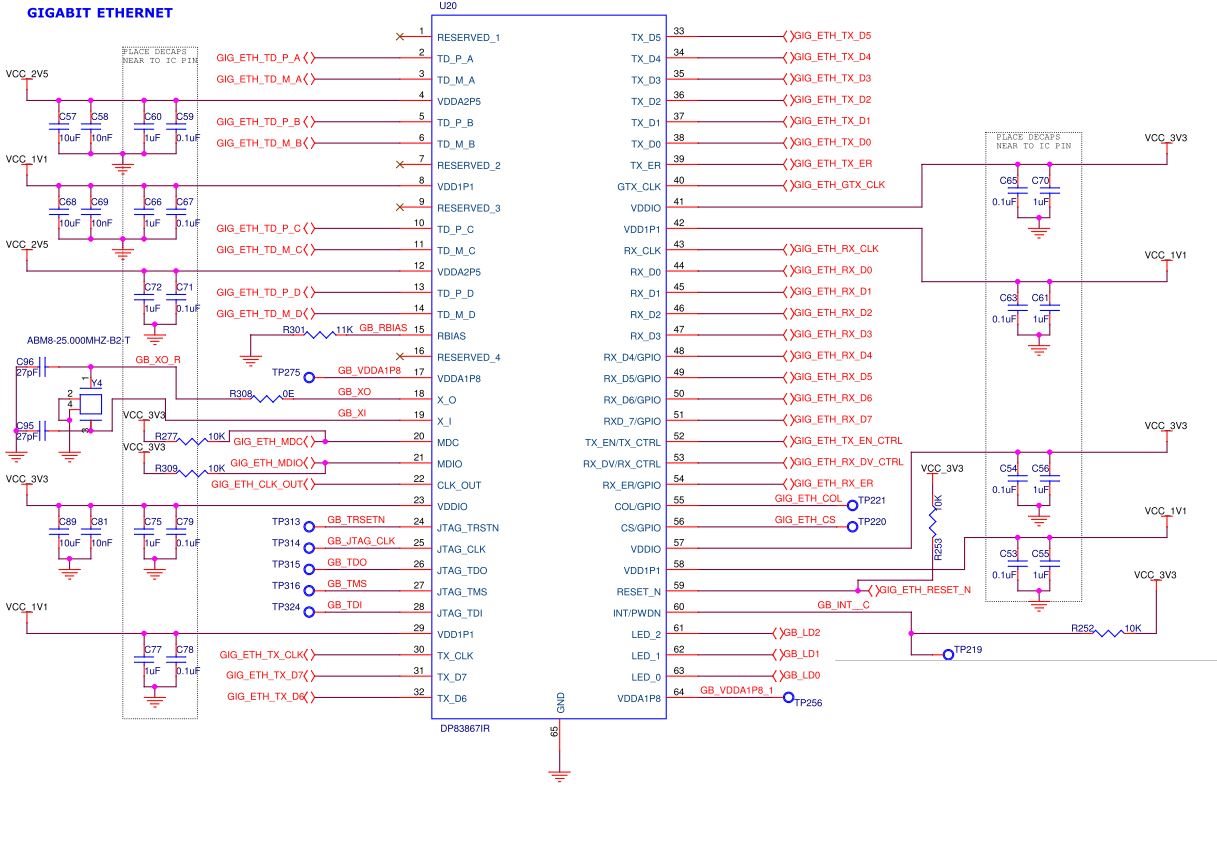

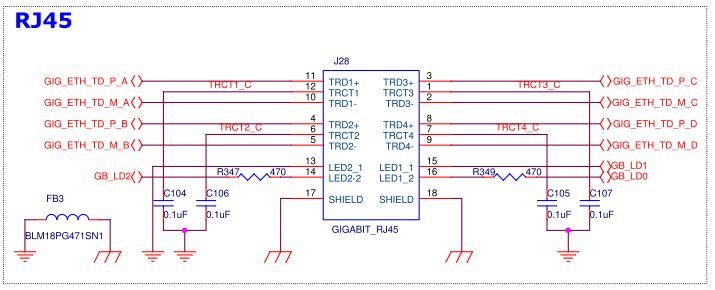

I am using DP86867IR as PHY interfacing with FPGA board and connected to PC on the other side. PC is configured to 100 Mbps full duplex communication.

Following is the issue I am observing:

1. After reset through 0x1F = 0x8000; I see link going up and messages on the ethernet monitoring tool. Probably because Auto negotiation is activated and hence getting link up.

But in case, Auto-negotiation is disabled after hard reset and try to set fixed rate of 100 Mbps, Link does not come up. Could you please let me know the possible root cause or proper sequence?

2. How much time should I wait after Reset to access/modify the MDIO registers? From datasheet, I could conclude 200 ms, but for safe side I am putting delay of 500 ms before accessing MDIO registers to set fixed link rate. Is it okay?

and the most important questions is:

3. After having link up, I can receive data on the MAC, but data transmitted from MAC are not shown on the Ethernet monitoring tool.

For 10 Mbps link speed, I can see data on the tool. Can you guide me through to solve this issue?

Please let me know, if you need any other information!

Thank you,

Hardik