Other Parts Discussed in Thread: THVD1500

Hi Team,

I received the following request:

################################

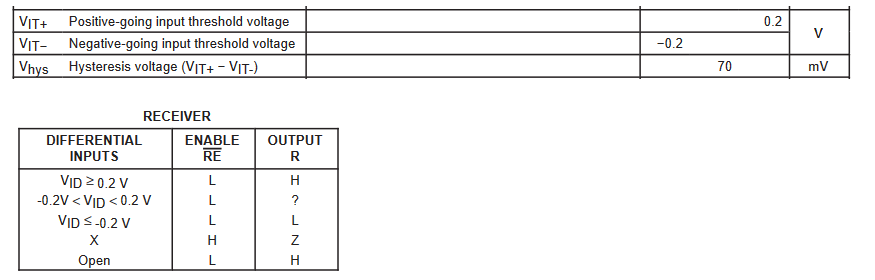

We have problems with RS485 communication. We use TI SN65LBC182D component. When the line is idle (master and slaves are on bus and in receive mode), RO (receive output) is not logic 1 always.

Above indeterminate condition (marked with ?) causes RO to random case. TI defines this condition as fail-safe condition. Below schematic is our master device. When the bus is in idle, Vid is always near to 0 V. This is indeterminate state. We need logic 1 of RO output when bus is idle. Because the microcontroller cannot detect this error data frame.

Can you suggest me something or any TI component to solve this problem?

I am waiting your comments.

################################

Regards,

Fabio