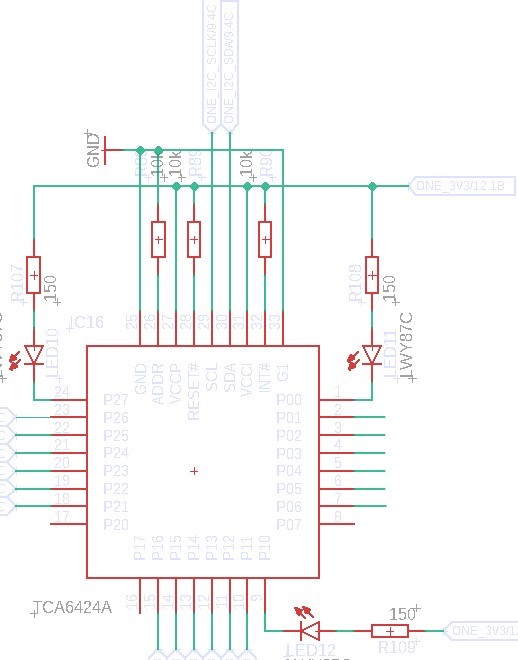

Part Number: TCA6424A

Dear support team,

I'm trying to get a TCA6424A to work. Sadly, it doesn't reply at all to I2C commands. Another slave on the same bus works without any problems. I would appreciate if you could point me at the thing I'm missing here...

This is a pic of the scope screen:

As you can see, the address byte doesn't get ACK'd.

This is the schematic:

As I'm running out of ideas, I'd really appreciate some help here!

Thank you!

Best regards

Lennart