Part Number: SN65LVDS93

Other Parts Discussed in Thread: SN75LVDS84A

Hi Team ,

my customer is using SN65LVDS93 as solution and have below 2 questions

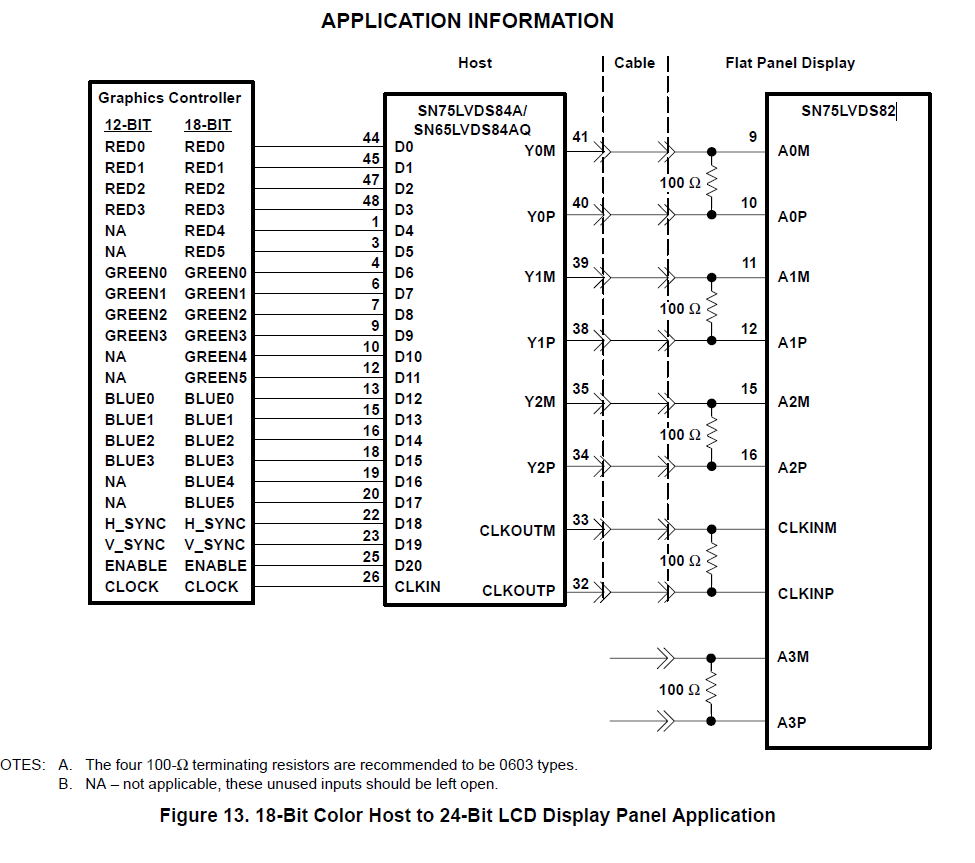

1. they have been use SN75LVDS84A(21:3) before , now they are using SN65LVDS93(28:4) for new project ,

so is the pin D24~D27 is used as below SN75LVDS84A d/s shown? And reference application pic in SN65LVDS93's d/s for my customer reference?

per my assume is yes , SN65LVDS93(28:4) should be same functionality with SN75LVDS84A(21:3) , just with more input .

2. About CLKSEL pin,if customer's Graphics Controller didn't have this pin to connect with ,where's should CLKSEL pin(即第17Pin) connect?

Can it left floating? if yes, in this condition the clock valid is at the rising or falling edge?

please kindly help on the questions above , thanks in advance!

Andy