Hi Team,

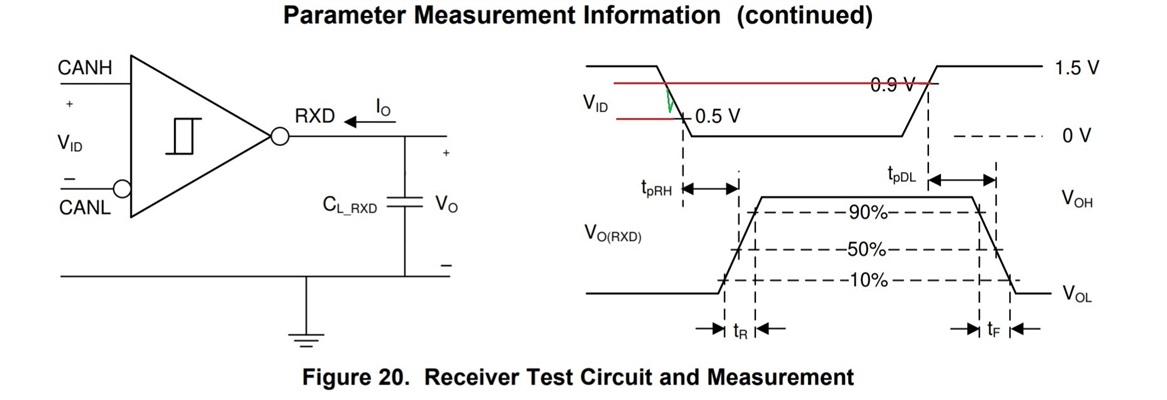

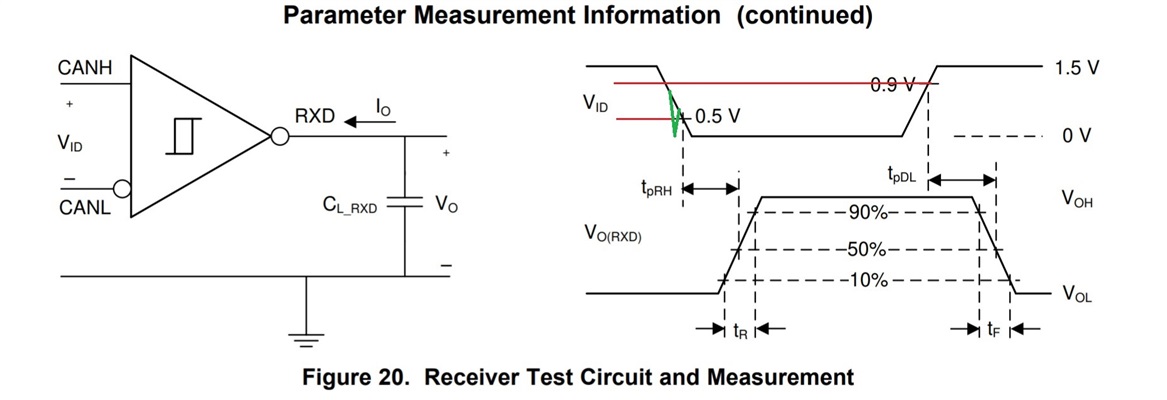

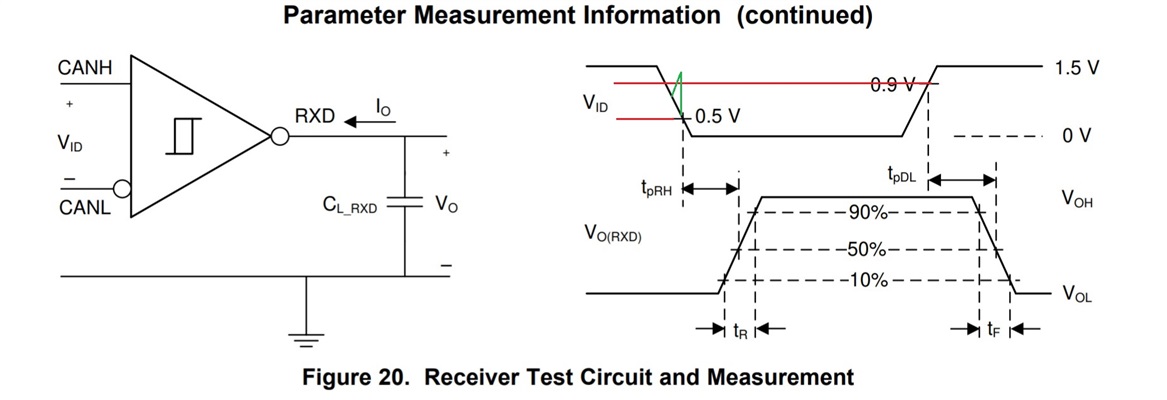

When TCAN334 is for receiver, if there is glitch on VID and the glitch voltage is between 0.5V and 0.9V shown in picture below, will the Vo(RXD) keep the same without change?

If the glitch voltage is below 0.5V or above 0.9V shown in picture below, may I know:

1. Will the Vo(RXD) change?

2. If the answer for item is yes, what's the minimum time requirement for the glitch voltage below 0.5V or above 0.9V?

Thanks and Best Regards!

Hao