Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869

Hello,

I have a custom design and I am struggling to get the data link. The PHY and network card can detect cable and link, but cannot send the data (get IP from DHCP or perform ping).

DP83869HM is used to interface with Fiber SFP module. The RGMII interface is connected to LAN7801 that is connected to computer via USB. I can access the PHY (DP83869HM) registers through command line interface from win 10. I read PHYIDR1 0x2 register well with value 0x2000. The SFP modules and cable were verified on different devices.

The current state is, that link is up what I can see from computer that design is connected to and also from router with another SFP module. The router is set up to auto-negotiation for all modes 10M to 1G.

Here are my questions:

1. A potential issue might be with detecting strapping option. I have the setting for RGMII to 1000Base-X with autonegotiation on and LOS detection on (JTAG_TDO pin - 2.5k pullup, RX_D3 open, RX_D2 open, LED_0 - pulldown, LED_1 - pullup), but I read 0x0000 from 0x6E register. What could be reason for wrong detection of strapping options?

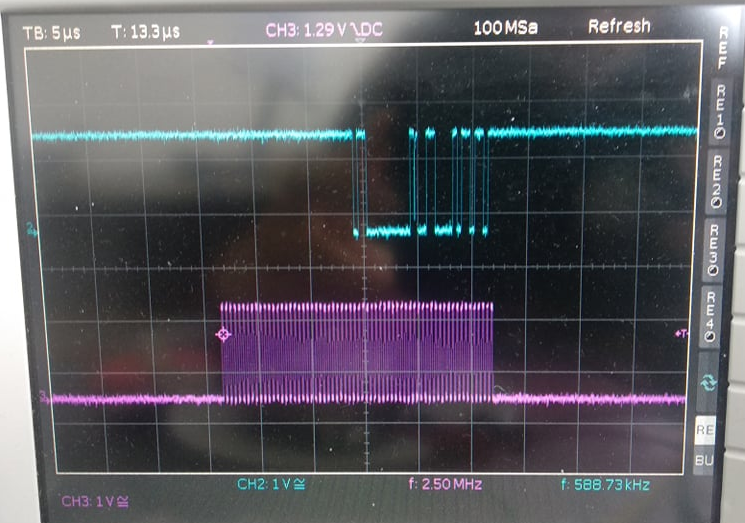

2. I suspect that RGMII might not be configured properly: MAC IC (LAN7801) has RGMII version 2. I measure 125MHz on RGMII TX and RX clock signals. I also see some data on RX and TX bus seconds after power-up. DP83869HM has RGMII delay enabled as default after reset 0x32 register value is 0x0000 (correct). The ANA_RGMII_DLL_CTR 0x86 register holds 0x0004 (should be default 0x77). After successful write of 0x77, I read back again 0x0004. Why is there a different default value after reset and why I cannot change the value?

3. Document DP83869 1000Base-X Link Detection states that "link status is stored in the FX_STS register bit [1]" whereas DP83869 datasheet says it is bit[2] of the FX_STS register. Is link status bit 1 or bit 2 in FX_STS register? If it is bit 2 then I read LINK STATUS BIT = 1, SERDES SYNC STATUS BIT = 0, what is stated as "not applicable" in link detection document.

4. I am not able to download USB2MDIO GUI tool that works on launchpad. Is it freely available for download anywhere? It might help with a debug.

Do you please have some ideas what I can be missing and how I can make the design operational?

Please find the schematics excerpt and PHY register damp after power up below.

Schematics excerpt:

RGMII is connected to MAC LAN7801. MAC has reset output connected to PHY RESET_N.

PHY registers after power up and recognized link:

address : value 0x0000 :0x1000 0x0001 :0x616d 0x0002 :0x2000 0x0003 :0xa0f1 0x0004 :0x05e0 0x0005 :0x4060 0x0006 :0x0007 0x0007 :0x2001 0x0008 :0x0000 0x0009 :0x0200 0x000A :0x0000 0x000D :0x4007 0x000E :0x0000 0x000F :0xf000 0x0010 :0x5448 0x0011 :0xac02 0x0012 :0x0000 0x0013 :0x0400 0x0014 :0x29c7 0x0015 :0x0000 0x0016 :0x0000 0x0017 :0x0040 0x0018 :0x6150 0x0019 :0x4404 0x001A :0x0002 0x001E :0x0012 0x001F :0x0000 0x0025 :0x4060 0x002C :0x0000 0x002D :0x4007 0x002E :0x0000 0x0031 :0xac02 0x0032 :0x0000 0x0033 :0x0000 0x0037 :0x0040 0x0039 :0x4404 0x003A :0x0002 0x0043 :0xa0f1 0x004F :0xf000 0x006E :0x0000 0x0086 :0x0005 0x0134 :0x29c7 0x0135 :0x0000 0x0170 :0x5448 0x0180 :0x1000 0x0181 :0x616d 0x0182 :0x2000 0x0183 :0xa0f1 0x0184 :0x05e0 0x0185 :0x4060 0x0190 :0x5448 0x0191 :0xac02 0x0192 :0x0000 0x0193 :0x0000 0x0194 :0x29c7 0x0195 :0x0000 0x0196 :0x0000 0x0197 :0x0040 0x0198 :0x6150 0x0199 :0x4404 0x01A4 :0x05e0 0x01A5 :0x4060 0x01A6 :0x0005 0x01DF :0x0000 0x01E0 :0x1000 0x0C00 :0x1000 0x0C01 :0x616d 0x0C02 :0x2000 0x0C03 :0xa0f1 0x0C04 :0x05e0 0x0C05 :0x4060 0x0C06 :0x0005 0x0C07 :0x2001 0x0C08 :0x0000 0x0C18 :0x6150 0x0C19 :0x4404