Hello,

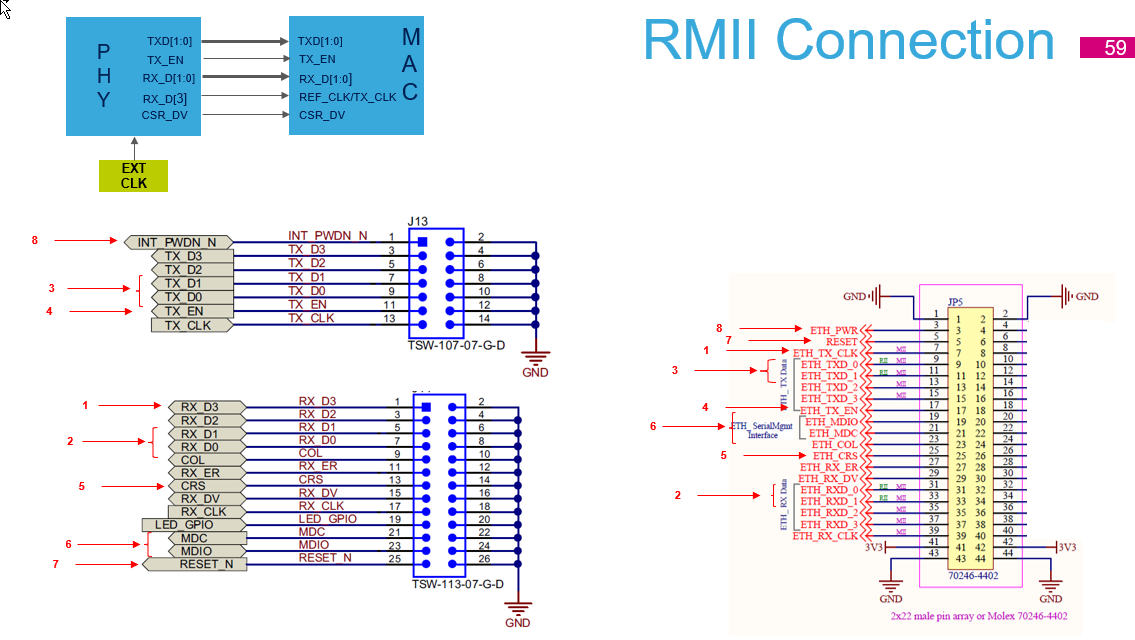

I am testing the RMII mode with my external MAC.

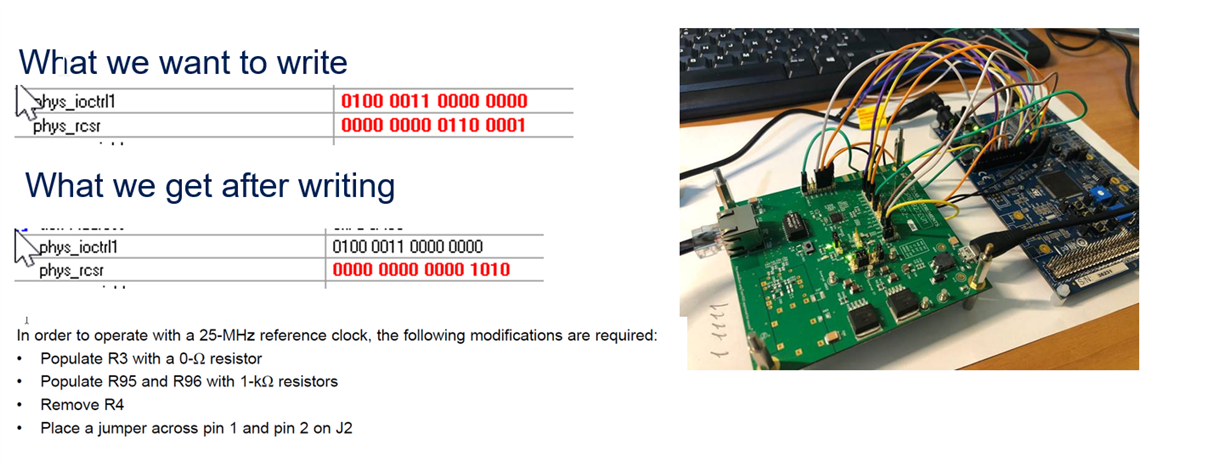

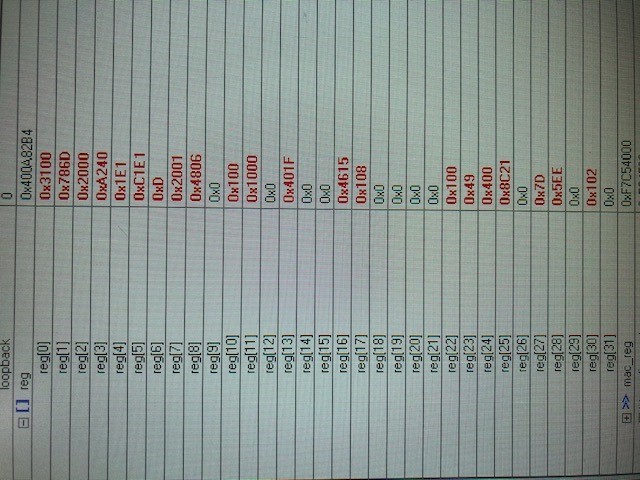

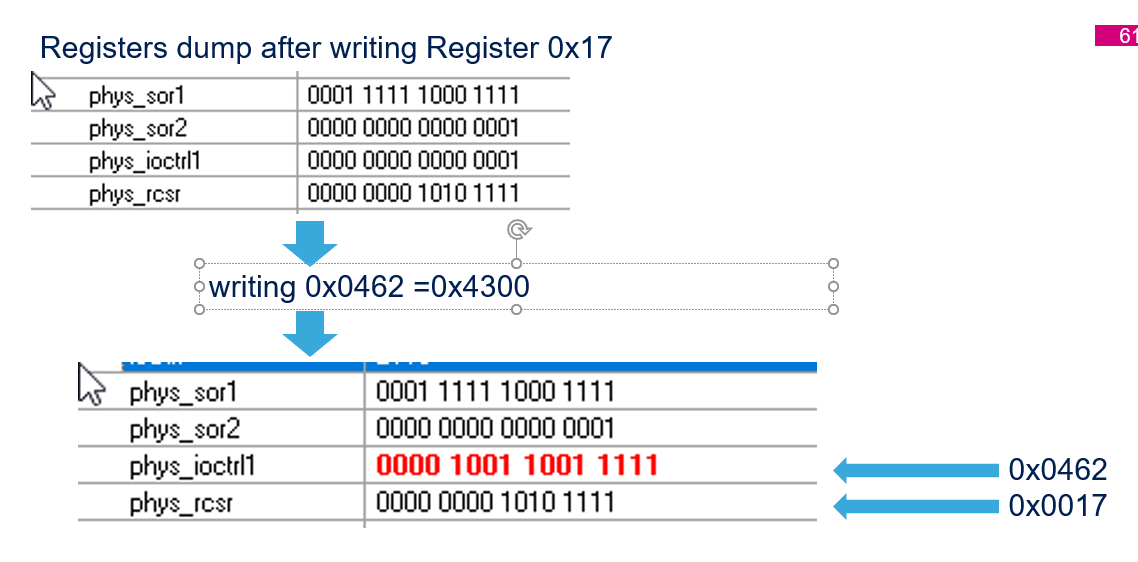

I followed everything I think should be followed in order to enable RMII, but I cannot manage writing RSCR correctly.

Phy is working in master mode with 25MHz clock.

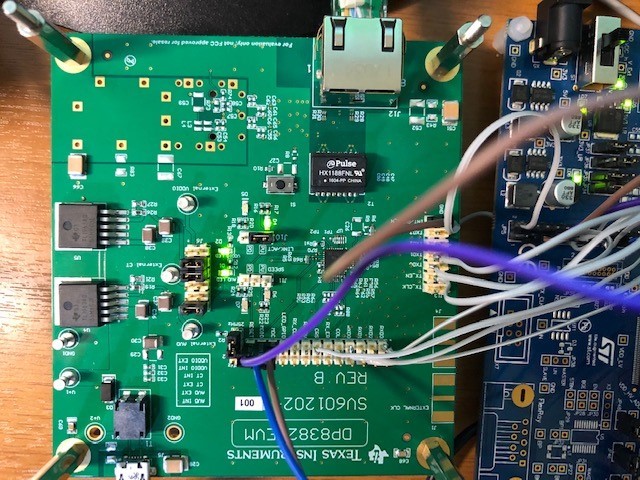

The only point I don't see compliant is the value of R3: in the board I got 18Ohm. I think it was put on purpose and maybe the shortage is in necessary.

I think we are missing something.

thanks in advance for your support.

Regards

GZ