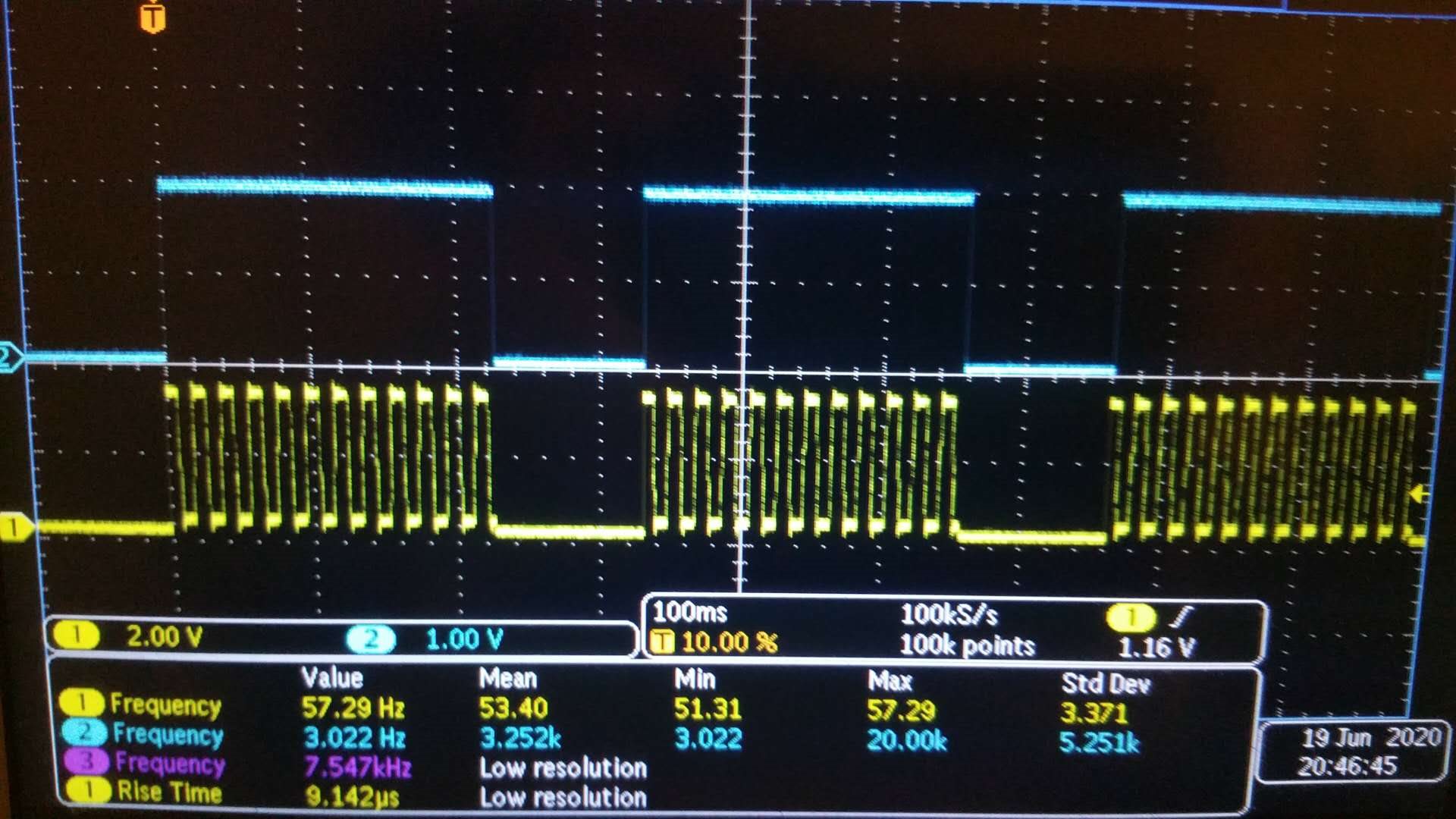

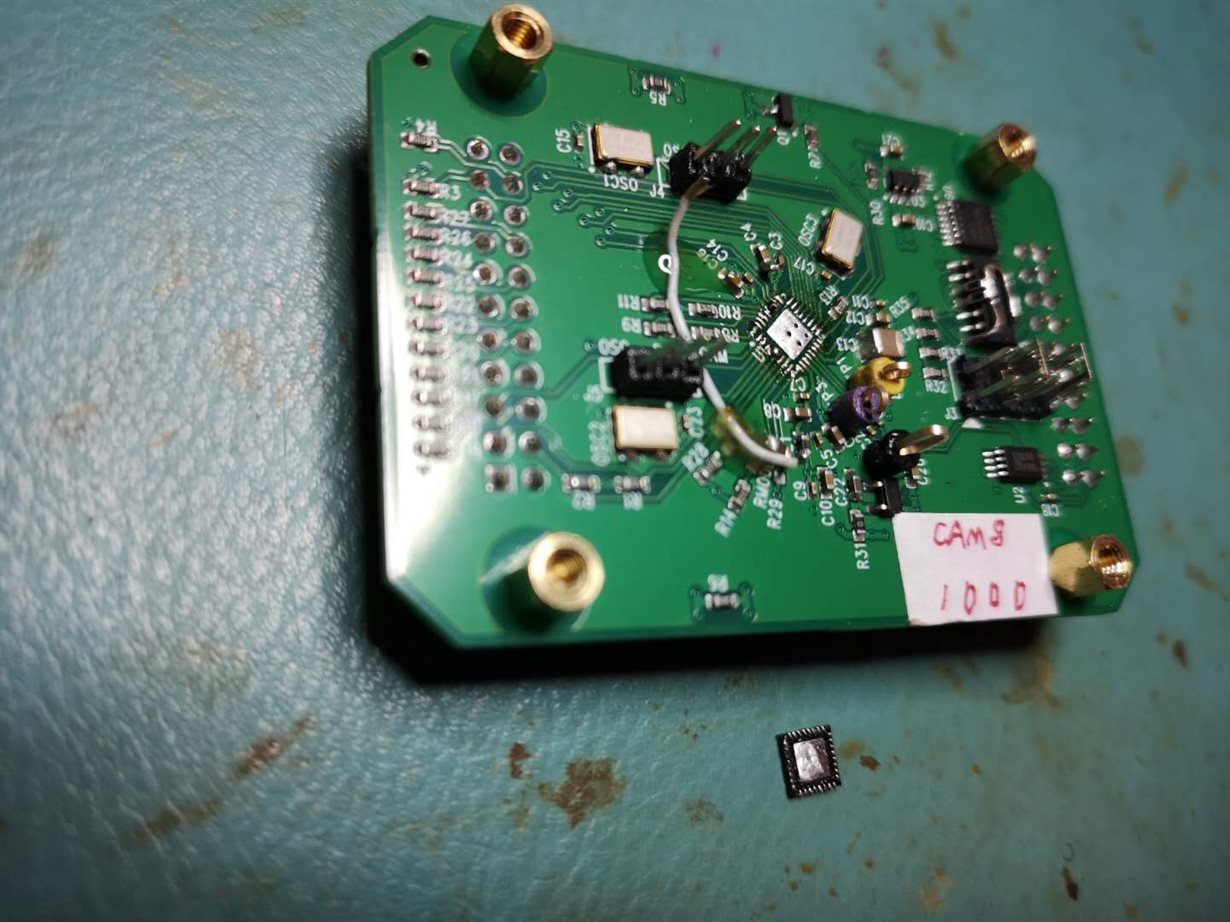

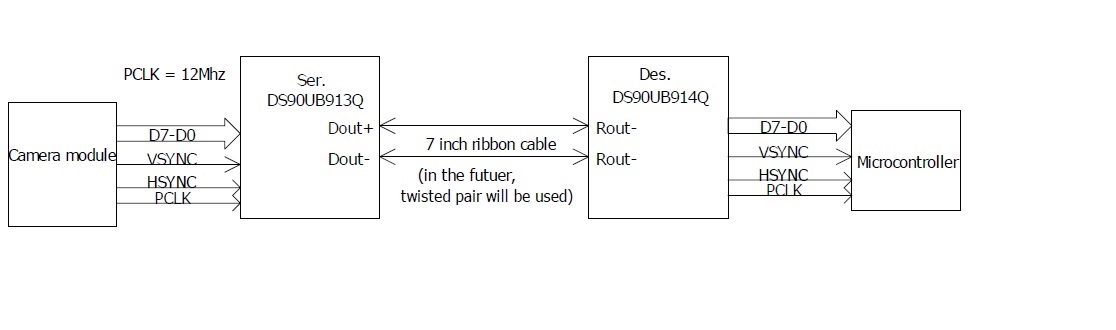

DS90UB914 and 913 work together, 914 is set to drive by PCLK.

when debugging , I found that PCLK must be always available, otherwise I2C communication to remote camera will be wrong, but when configuring the camera, PCLK may be not available for a moment, should software check pass and lock signal to before I2C communication?

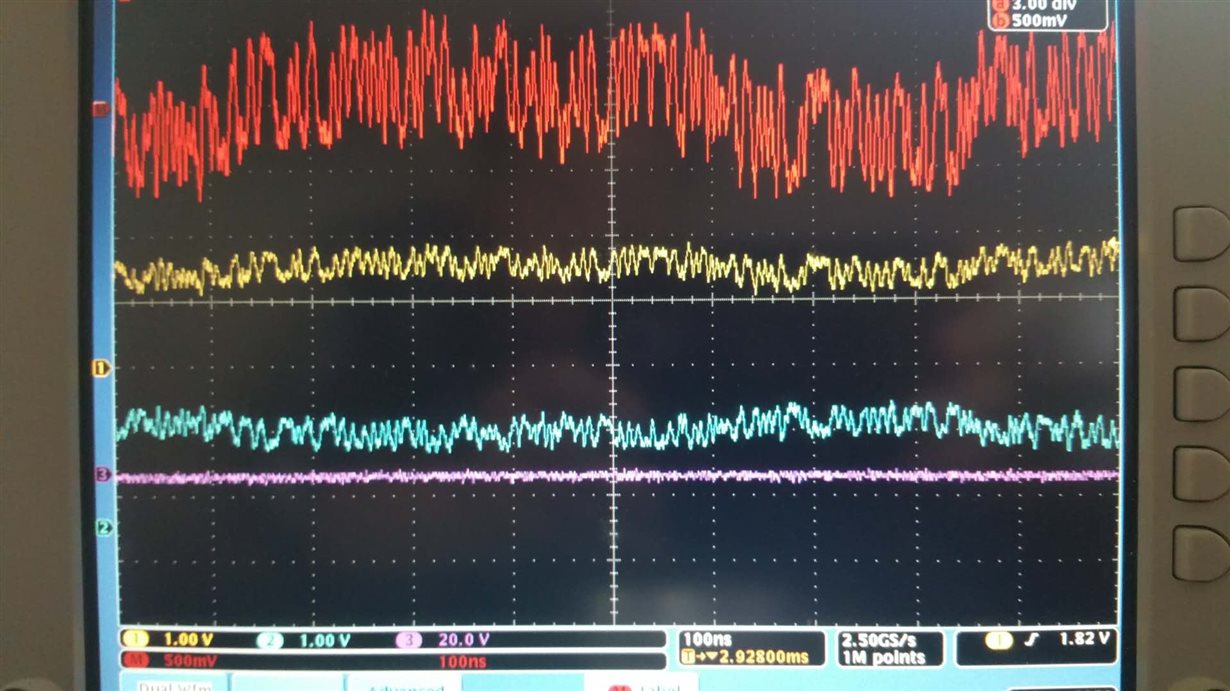

2) some camera module can set a few PCLK speed, so, in case pixel data is making the camera buffer full, PCLK can change to high frequency to send out pixel data faster, in this situation, will 913 and 914 still be working stable? thanks