Other Parts Discussed in Thread: BQ35100,

Hi team,

My customer is doing EDVT testing in their project, they found the MCU I2C (EFR to I/O Expander ) communication timing can not meet the spec.

See below pictures for details . Please help to double check if it is acceptable. And looking forward to your feedback.

Thanks

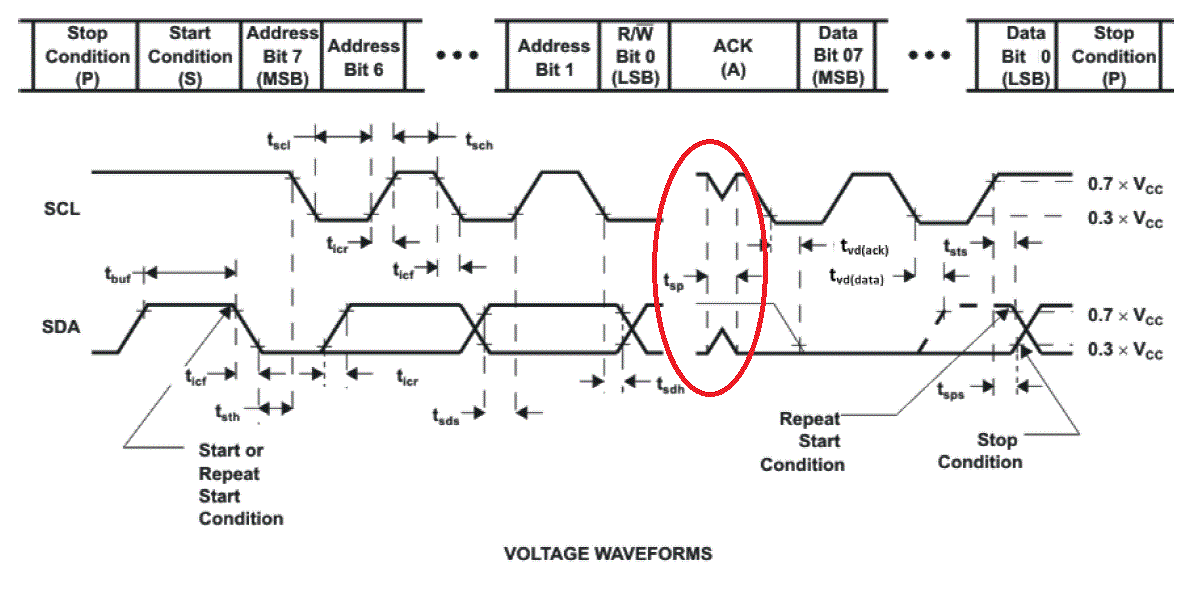

The tsp: spike timing diagram.

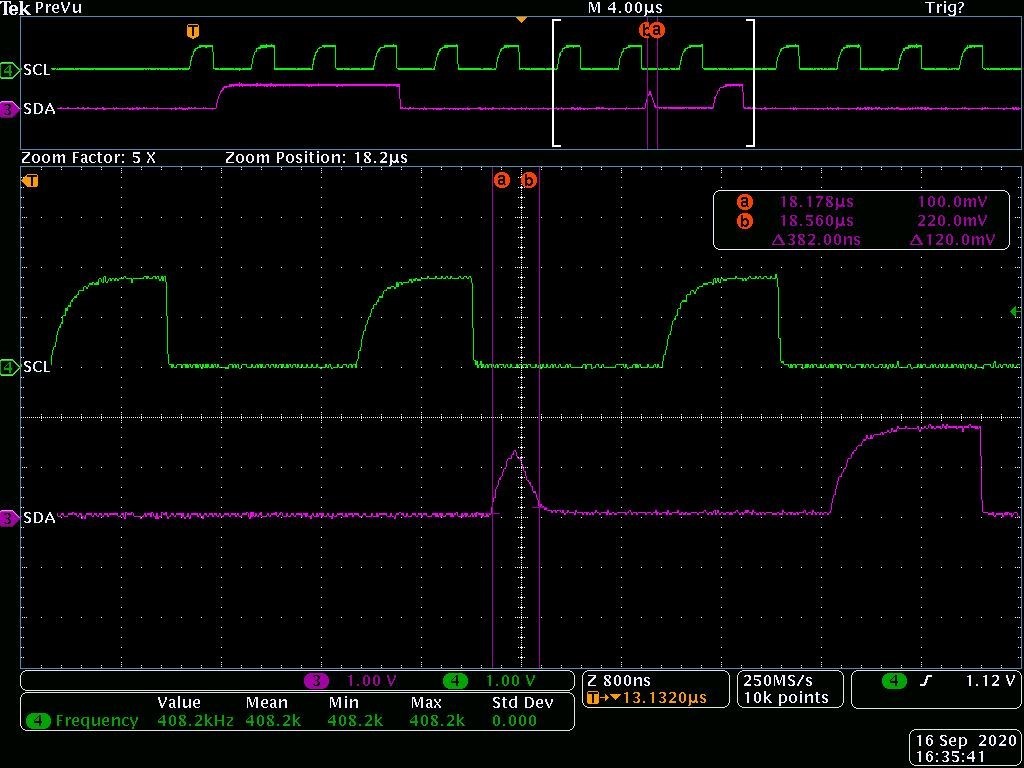

And customer's testing at 400kHz clock. The tsp is around 382ns that is larger than 50ns

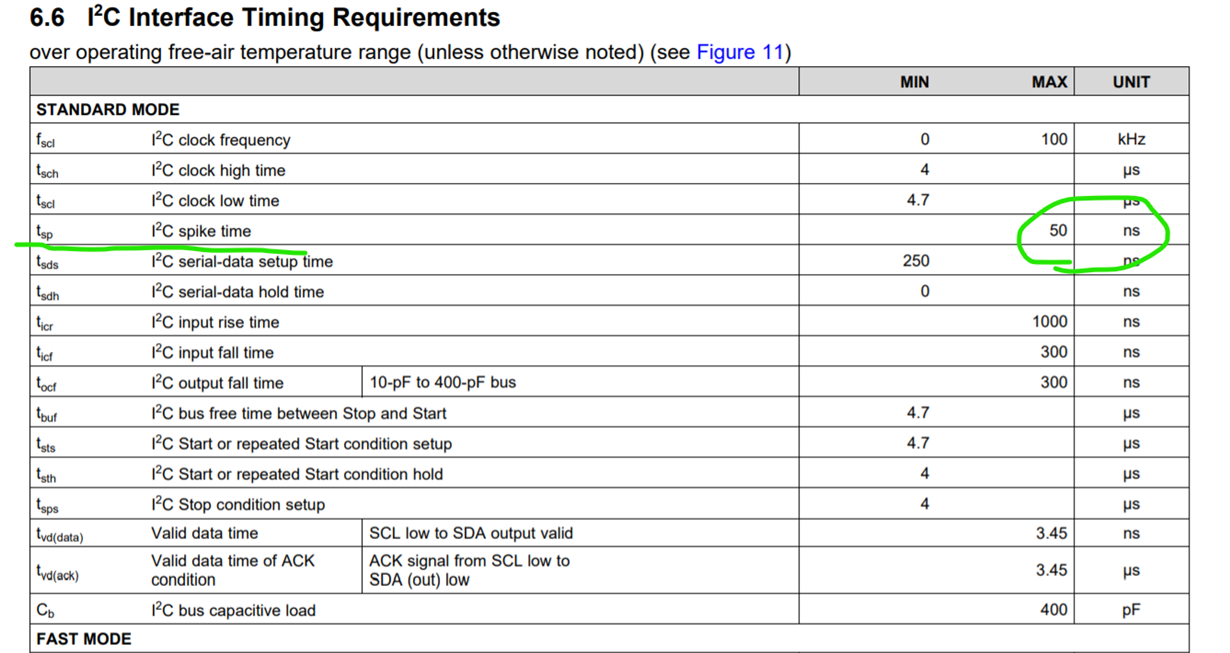

testing at 100kHz. The tsp is around 412ns that is larger than 50ns