Dear Technical Support Team,

I have been trying following issue.

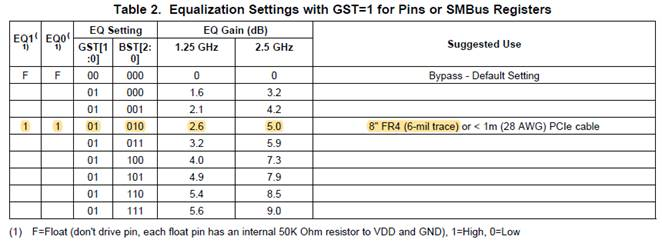

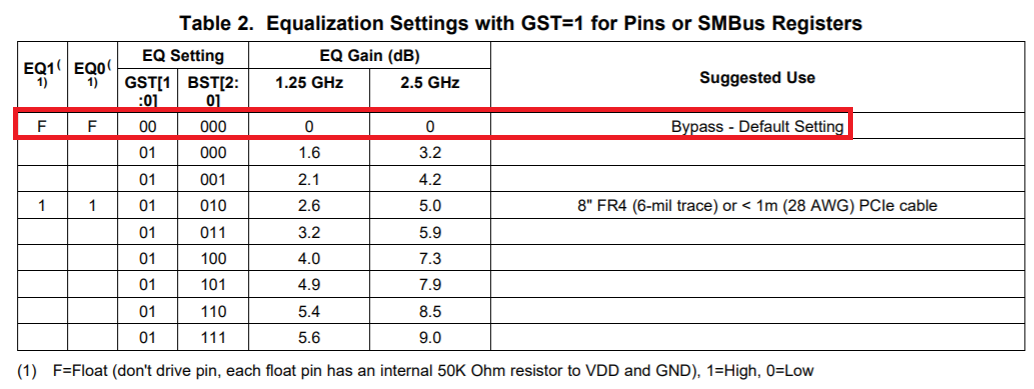

I tried various settings, but there was no combination to solve link up issue. It is NG even in Bypass mode.

Therefore, when DS50PCI402 was removed and connected with a patch wire, the link up issue was improved.

Is it possible that problems will occur if the wiring length is short?

Currently, the wiring length is within 10 cm.

Best Regards,

ttd