Other Parts Discussed in Thread: SN65DSI86, TEST2

Hi,

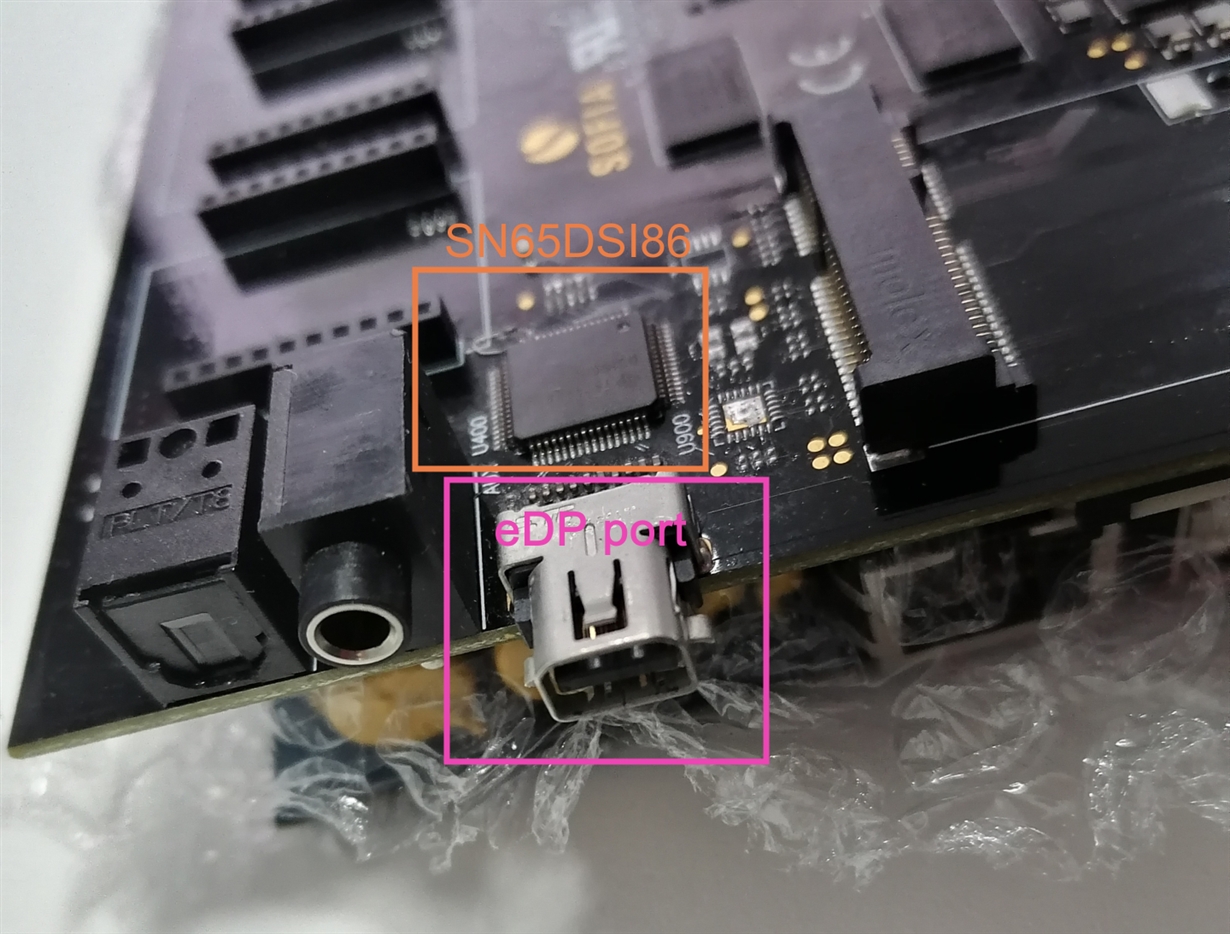

We are working with SN65DSI86 module on a custom IMX8MM board, we checked that the module is powered and enabled correctly.

The module is conencted to the I2C_1 bus.

When booting the Kernel, we check the presence of the module with "i2cdetect -a 0" but there is no module on 0x2d.

We tried to activate the SN65DSI86 driver in the Kernel 5.4.27 and patched the Kernel and Uboot DTS files like this:

sn65_bridge: sn65dsi86@2c {

#address-cells = <1>;

#size-cells = <0>;

compatible = "ti,sn65dsi86";

reg = <0x2c>;

ti,dsi-lanes = <4>;

max,dsi-channel = <1>;

ti,dp-lanes = <2>;

status = "okay";

enable-gpios = <&gpio1 9 GPIO_ACTIVE_HIGH>;

interrupts-extended = <&gpio1 10 IRQ_TYPE_EDGE_FALLING>;

vccio-supply = <&ldo6_reg>; //1.8V

vcca-supply = <&buck1_reg>; //1.2V

vpll-supply = <&ldo6_reg>; //1.8V

vcc-supply = <&buck1_reg>; //1.2V

clock-names = "refclk";

clocks = <&clk IMX8MM_CLK_DSI_CORE>,

<&clk IMX8MM_CLK_DSI_PHY_REF>;

panel@0 {

reg = <0>;

pinctrl-0 = <&pinctrl_mipi_dsi_en>;

enable-gpio = <&gpio1 9 GPIO_ACTIVE_HIGH>;

panel-width-mm = <68>;

panel-height-mm = <130>;

port {

panel1_in: endpoint {

remote-endpoint = <&sn65_out>;

};

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

sn65_in: endpoint {

remote-endpoint = <&dsim_to_sn65>;

};

};

port@1 {

reg = <1>;

sn65_out: endpoint {

data-lanes = <0 1 2 3>;

lane-polarities = <0 1 0 1>;

remote-endpoint = <&panel1_in>;

};

};

};

};

&mipi_dsi {

status = "okay";

port@1 {

dsim_to_sn65: endpoint {

remote-endpoint = <&sn65_in>;

attach-bridge;

};

};

};

We didn't do anything with Uboot to add the video variable to bootargs for the moment.

After these modifications this error shows:

# dmesg | grep drm [ 0.894170] imx-drm soc@0:bus@32c00000:display-subsystem: no available port [ 4.229399] [drm:ti_sn_bridge_probe [ti_sn65dsi86]] *ERROR* could not find any panel node [ 4.270746] [drm:ti_sn_bridge_probe [ti_sn65dsi86]] *ERROR* could not find any panel node [ 4.353747] [drm:ti_sn_bridge_probe [ti_sn65dsi86]] *ERROR* could not find any panel node [ 4.432826] [drm:ti_sn_bridge_probe [ti_sn65dsi86]] *ERROR* could not find any panel node [ 4.673391] [drm:ti_sn_bridge_probe [ti_sn65dsi86]] *ERROR* could not find any panel node [ 4.682721] [drm:ti_sn_bridge_probe [ti_sn65dsi86]] *ERROR* could not find any panel node

- Is there a problem with the module that it can't be shown in i2cdetect?

- Is the DTS file correct?

- Do we need to port Uboot to VIDEO support for it?

Thanks, Talel