Hi,

Below is mentioned on the datasheet;

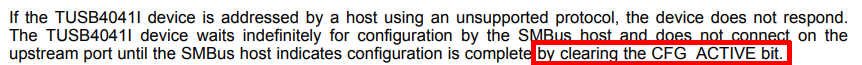

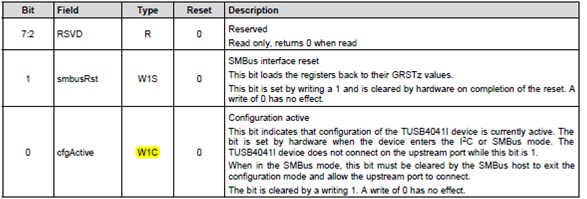

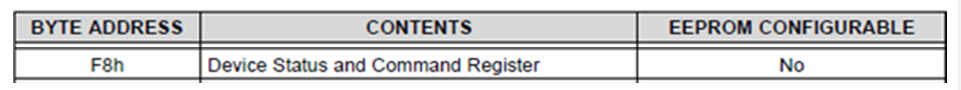

"The TUSB4041I device waits indefinitely for configuration by the SMBus host and does not connect on the upstream port until the SMBus host indicates configuration is complete by clearing the CFG ACTIVE bit".

"The bit is cleared by a writing 1."

I'm understanding that CFG ACTIVE bit should be written 1 to complete configuration.

On the other hand, there is below mention on the datasheet.

"TUSB4041I device does not connect on the upstream port while this bit is 1."

So I worry that the upsteram port is not connected by clearing the CFG ACTIVE bit.

Do I misunderstand?

Best Regards,

Kuramochi