Hi team,

we have two question about DDC bus.

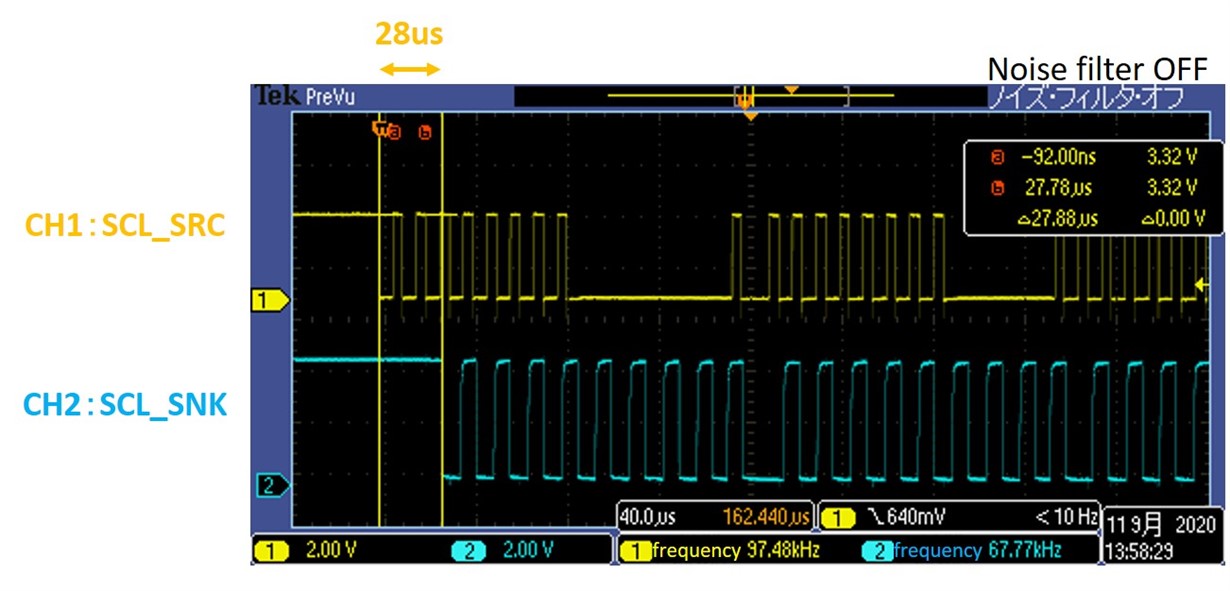

1. Our customer input 100kHz clock to SCL_SRC, but SCL_SNC output about 70kHz like follow figure 1.

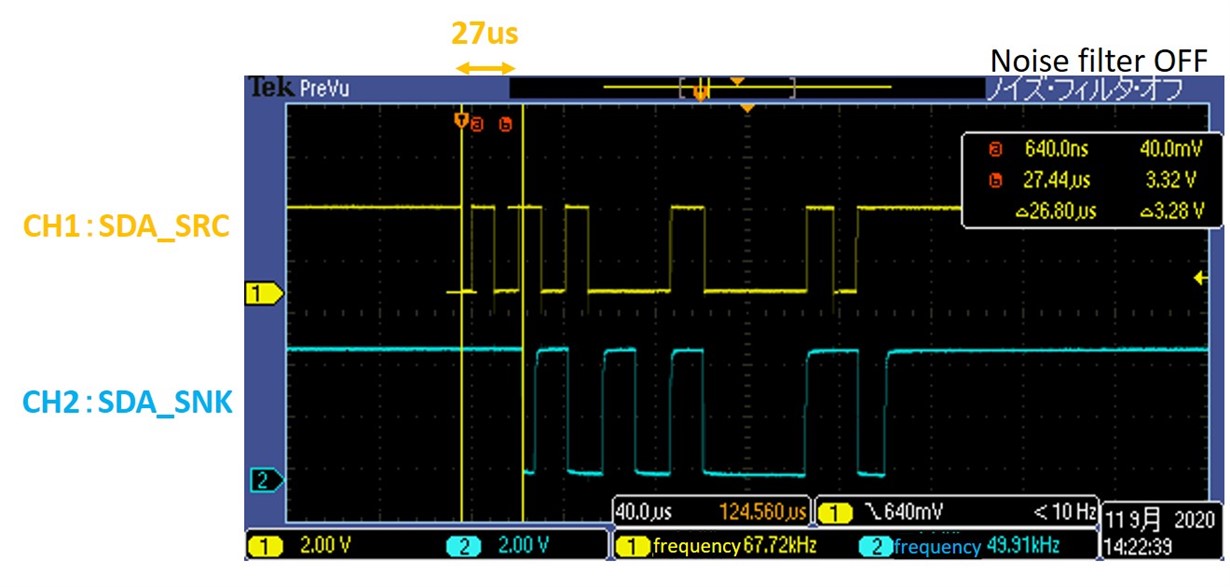

This frequency translate occurred at SDA_SRC/SDA_SNK too like figure 2.

They want to translate only voltage level from 3.3V to 5.0V with same frequency.

Can TDP158 be used like this ?

Is there any cause of this you can think of ?

2.Between input SCL_SRC and output SCL_SNK, there is about 28us propagation delay.

In data sheet, says "When the TDP158 detects the start condition on the DDC bus from the SDA_SRC/SCL_SRC it transfers the data or clock signal to the SDA_SNK/SCL_SNK with little propagation delay.".

Can this propagation delay be recognize as a characteristic of the device?

figure1.

figure 2

best regards,

teritama