Other Parts Discussed in Thread: TDA2E

Dear team,

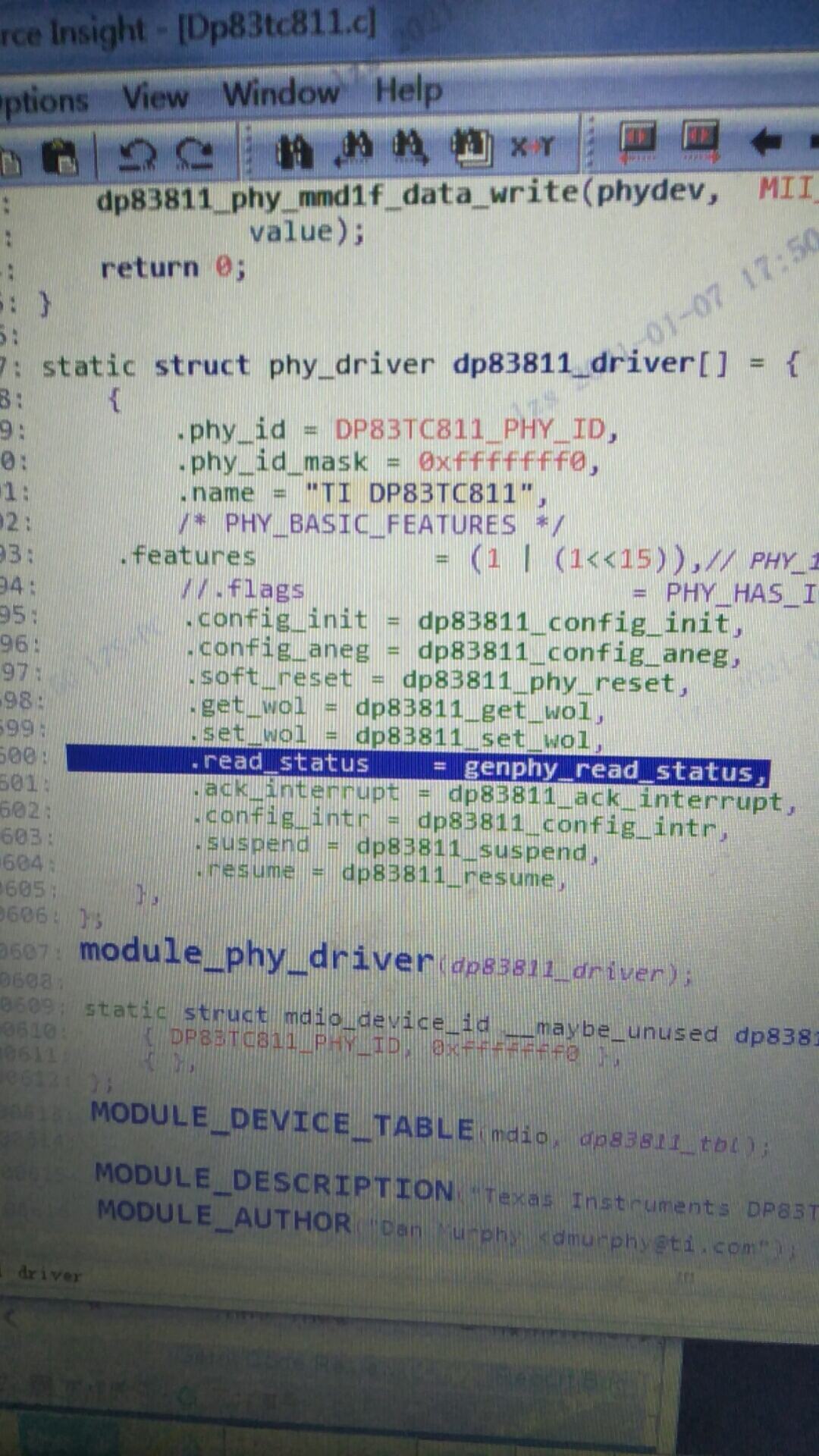

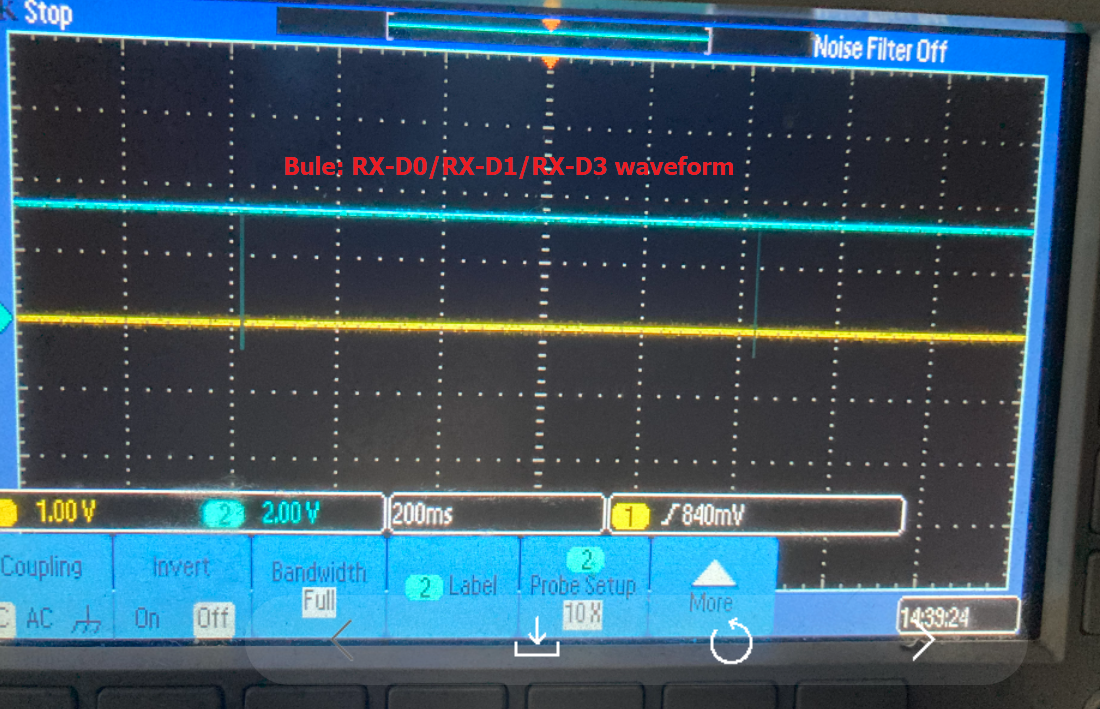

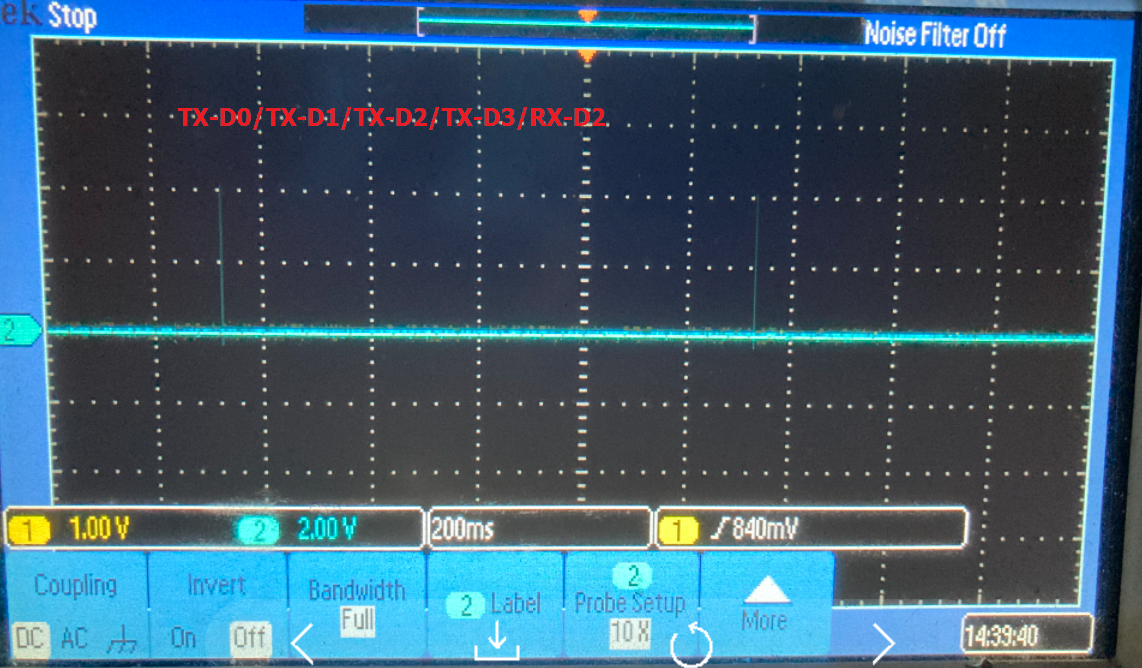

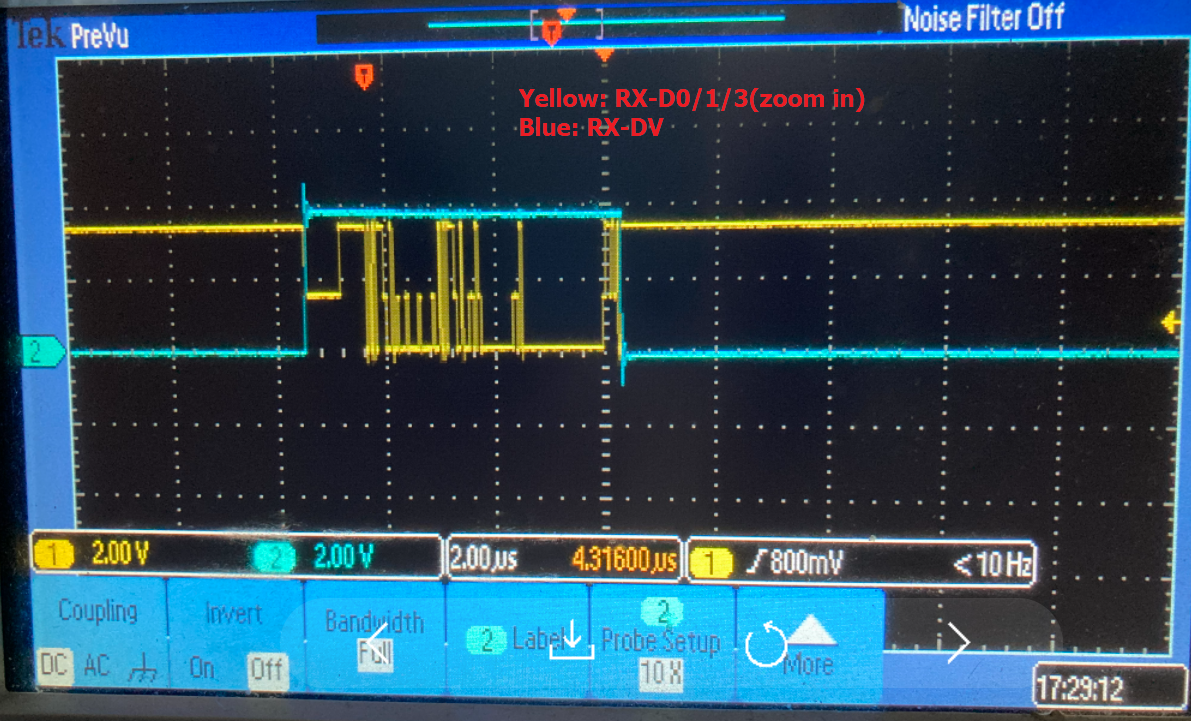

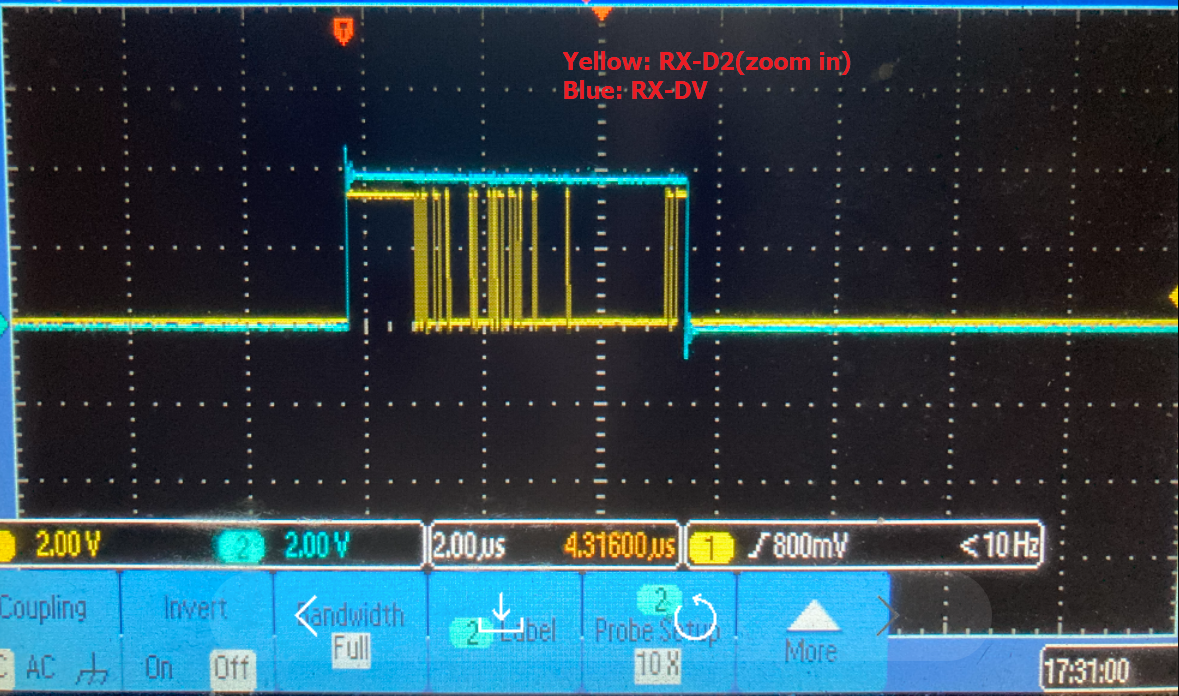

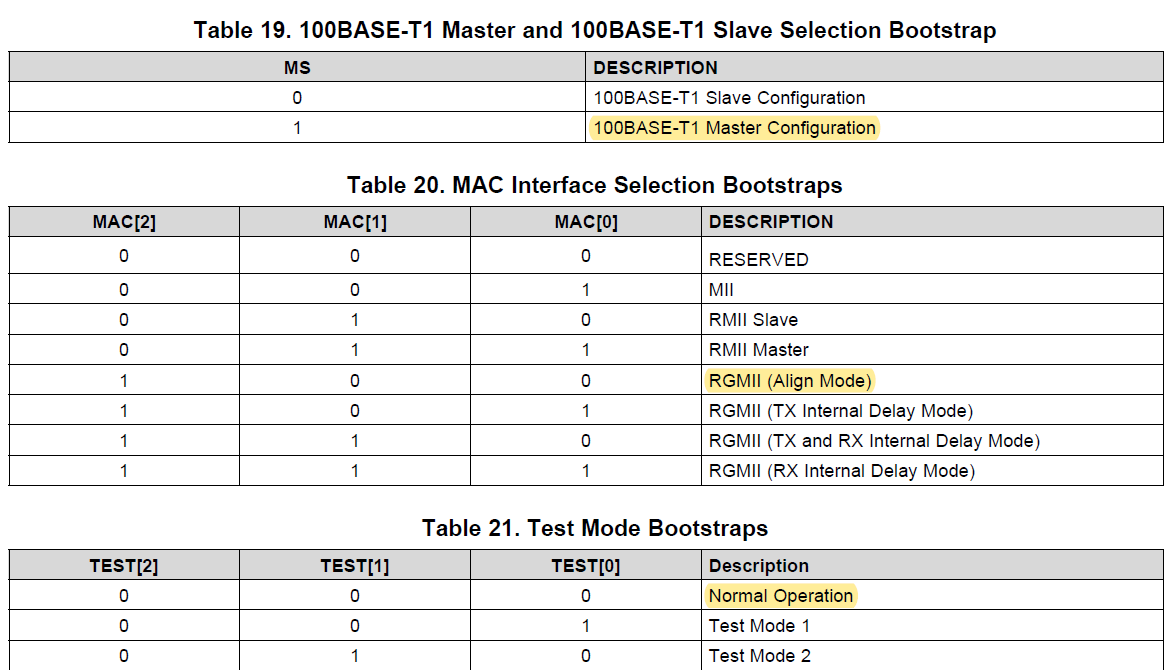

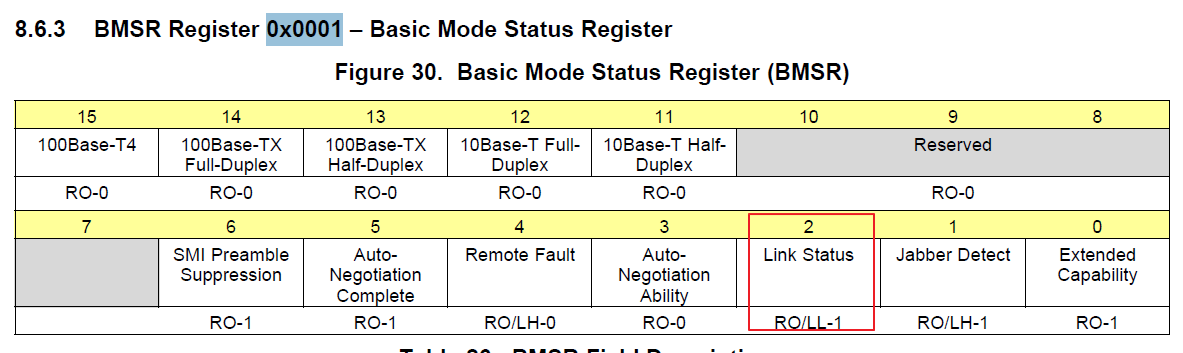

My customer use DP83TC811R-Q1, RGMII, and the SOC is TDA2E. Currently based on our linux driver code as below link, they can read and write 811's registers, but Ping can't work, and at the same time, 811's 0x1 registers indicates no link. Could you please help analyze this issue?

driver code:https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/tree/drivers/net/phy/dp83tc811.c

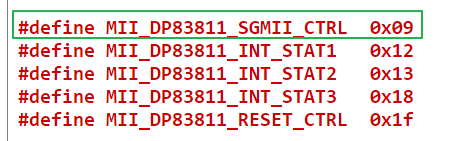

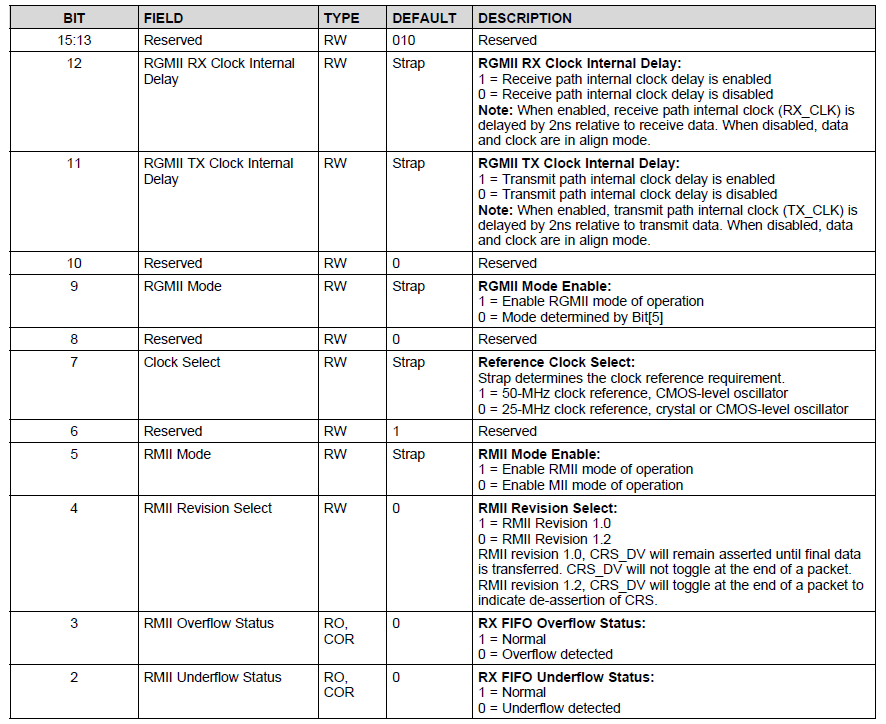

In my understanding, I just need to change the first line to ''#define MII_DP83811_RGMII_CTRL 0x017'', right?

Do we need to configure other registers of 811?

Thanks & Best Regards,

Sherry