Hi team,

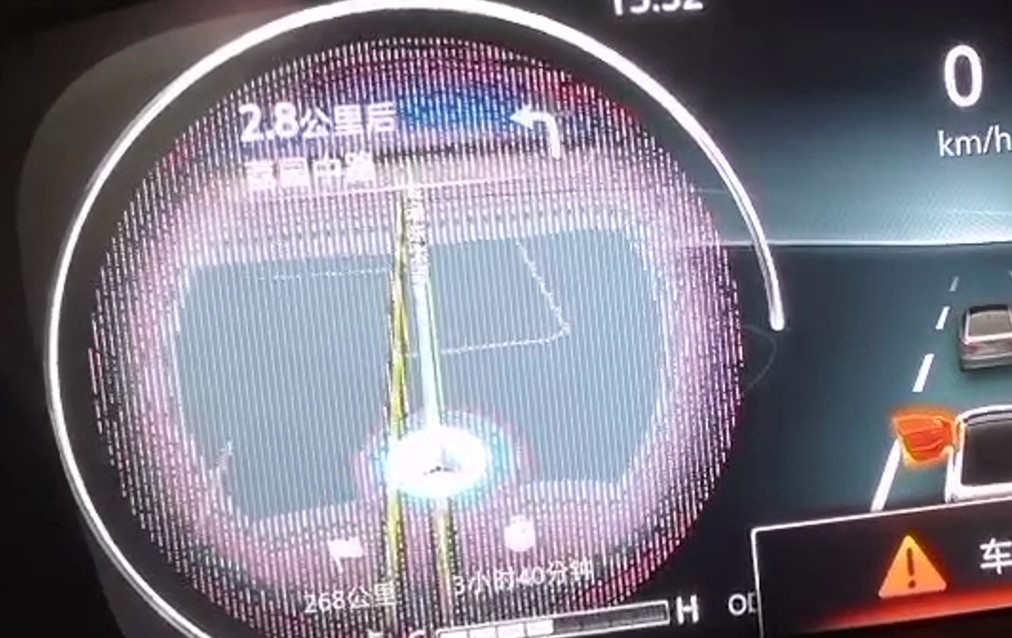

In 949/940 application, we found the display will splash sometimes in the end car oem. the LOCK and PASS status of 940 are high. if the LOCK goes to low, will reset 940.

there two 949 boards, A-SER of 949 is single output. only OUT0 have signal and OUT1 not. B-SER is dual mode, OUT1 &OU2 are the same. we suspect the 949 LVDS peformance is not good, which result in the 940 de-ser issue.

I attached customer eye diagram in A-SER board and B-SER board. could you help to check if it good for 940? and, in 940 side, how to change the setting to help solve splash issue, in 949 side, how to improve?