Other Parts Discussed in Thread: ALP, USB2ANY

Hi,

I have image sensor connected to DS90UB913 then via FPD-link III to DS90UB914. DS90UB914 is on my board and I2C lines are accessible. I would like run Margin Analysis Program (MAP) using an Analog LaunchPad software.

I meet a issue is that the ALP can't detect DS90UB914 via USB2ABY adaptor. Could you give some advices?

Background information :

1. I have read USB2ANY Interface Adapter User's Guide(SNAU228–January 2018), SNLA301–January 2019 and SNLU243–January 2019.

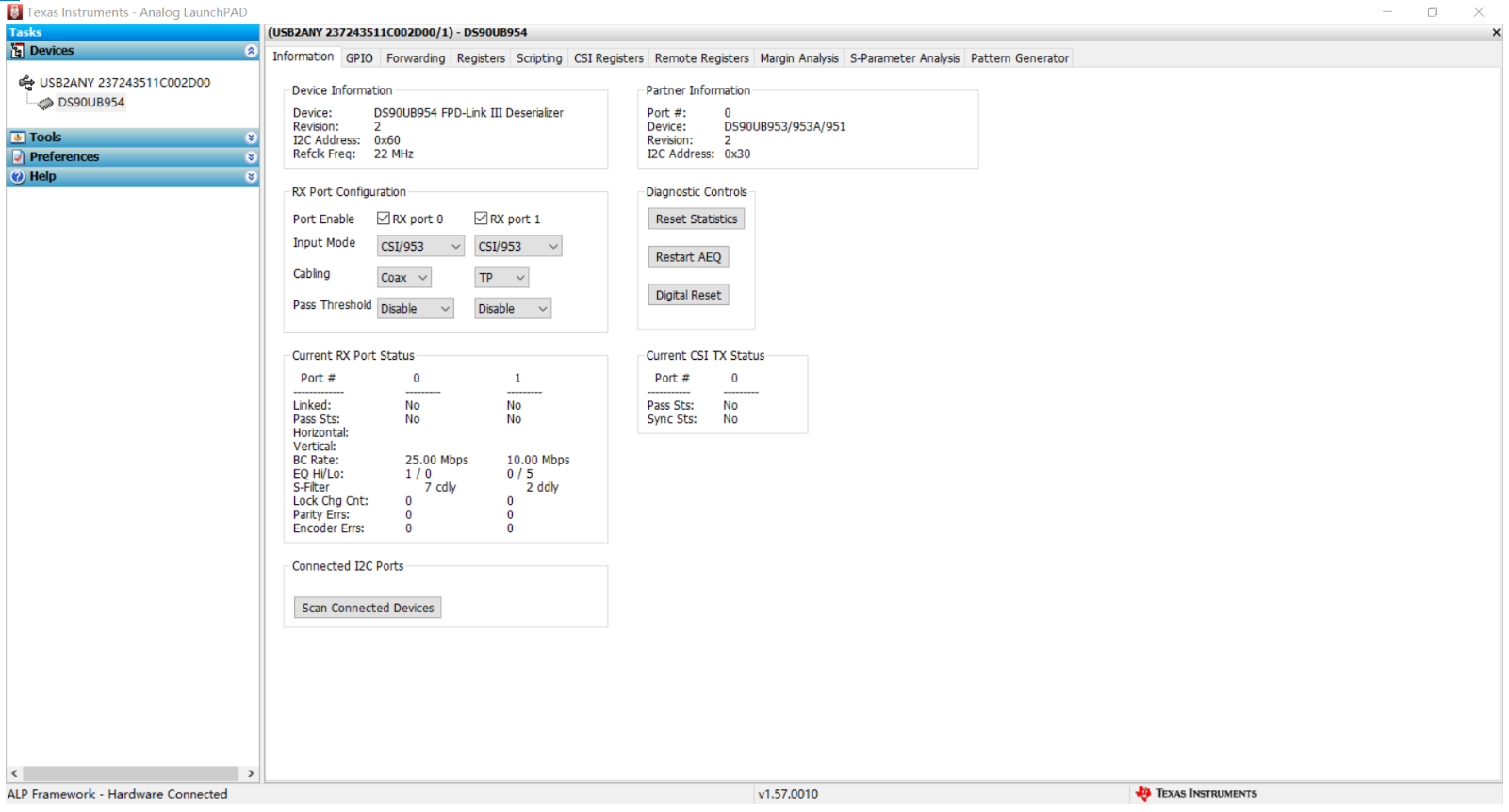

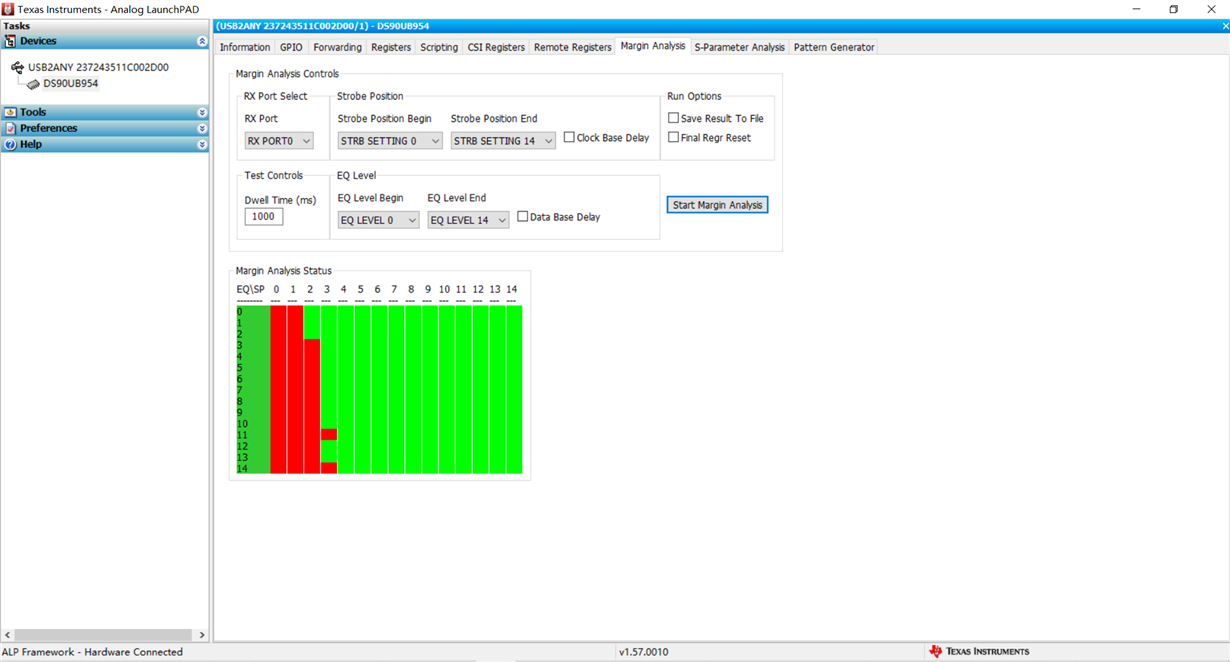

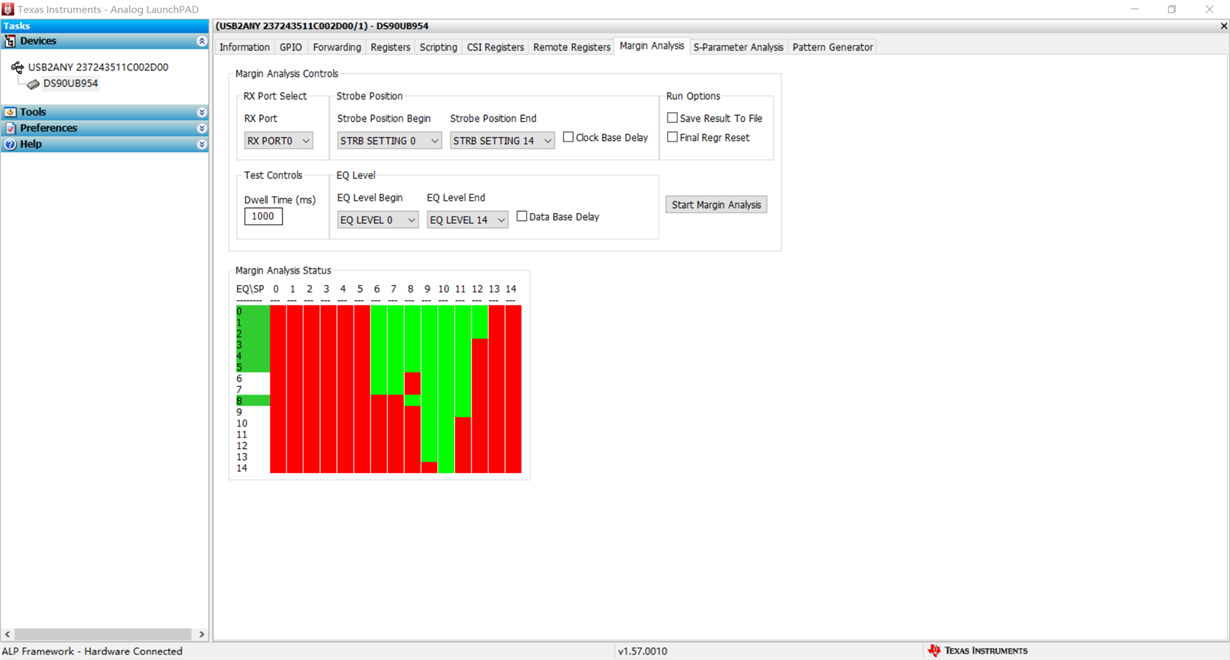

2. The ALP software version is v1.57.0010.

3. The USB2ANY adapter hw version is HPA665, firmware version is 2.7.0.0.

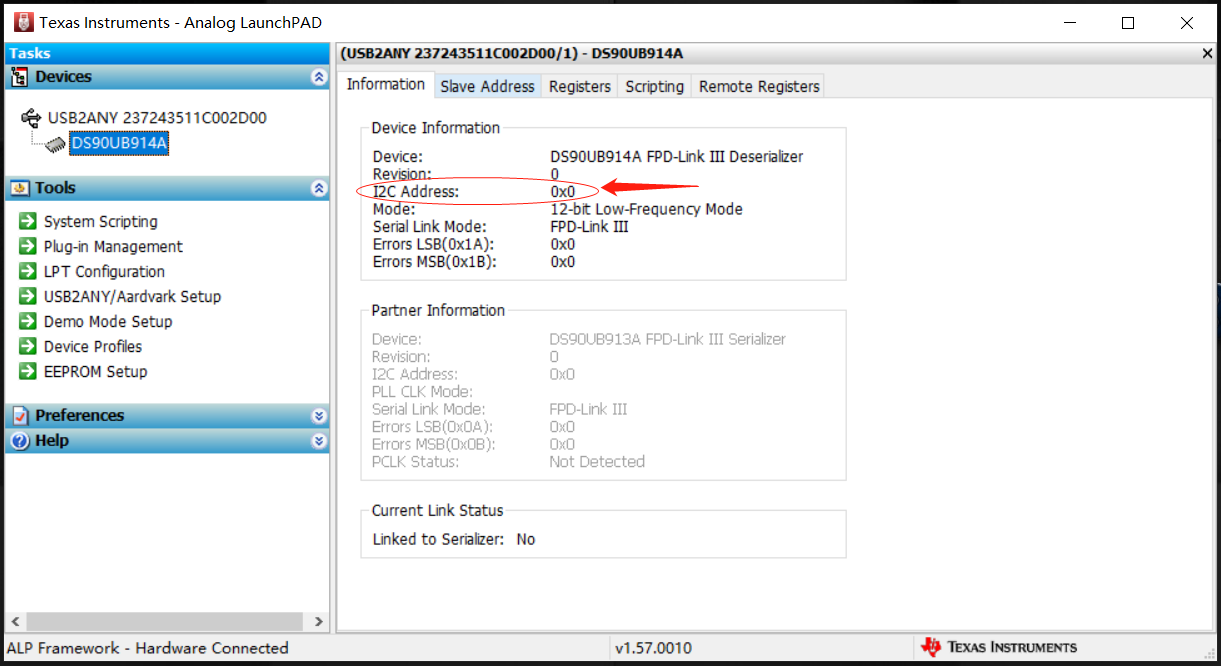

4. The system is: PC(ALP) --- USB2ANY adaptor(IIC) --- DS90UB914(IIC ID:0xC0)

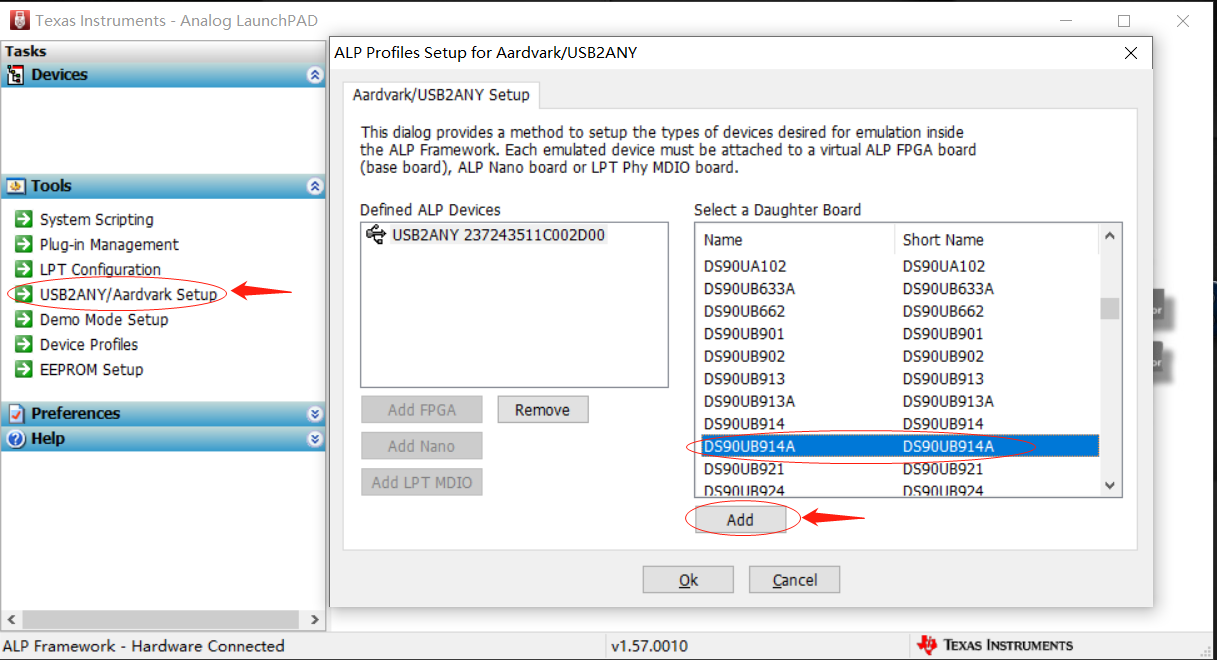

5. add deserdes frofile:

6. The ALP can't find deseredes: