Other Parts Discussed in Thread: STRIKE

Hi team,

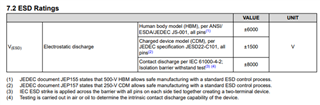

Could you help me to clarify the ESD specification of ISO6740?

I'd like to clarify the bias condition of each pins under the HBM and CDM tests.

In HBM and CDM, it is described as "all pins".

When the ESD strike is applied to the target pin, how the other pins are biased? Are they grounded?

Could you suggst related app note to help my undarstanding of the ESD test?

Best regards,

Itoh