Hi team,

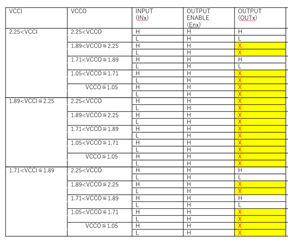

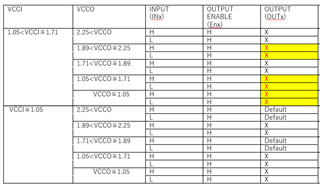

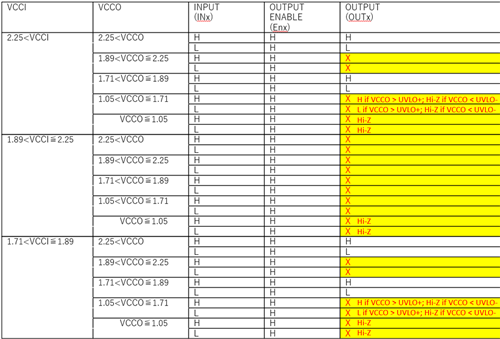

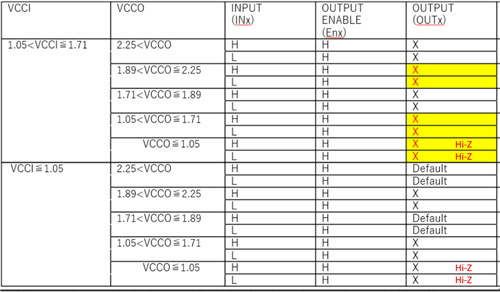

1. ISO67xxF output is undetermined when 1.89 V < VCCI, VCCO < 2.25 V and 1.05 V < VCCI, VCCO < 1.71 V.

My customer concerns that the case when VCCI or VCCIO ramp up or down slowly, the output can be undetermined.

Could you please advice how to avoid undetermined output?

Can you please let me know the reasonable ramp up or down rate to avoid undetermined output?

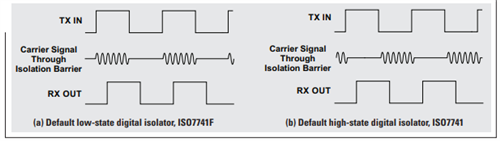

2. UVLO threshold is specified in the datasheet, but I don't find the detailed function from the datasheet.

Is it similar to powered down (PD) state described in datasheet 9.4?

Regards,

Itoh