Dears

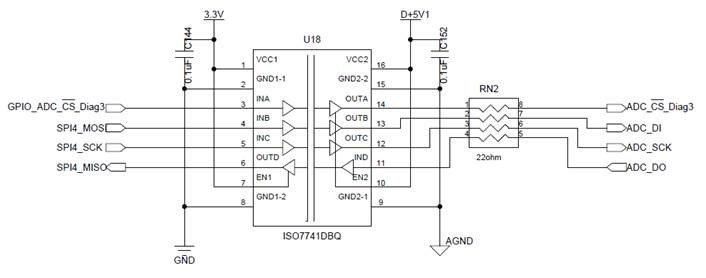

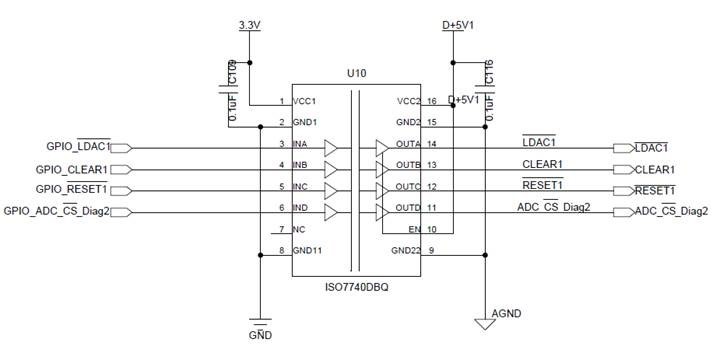

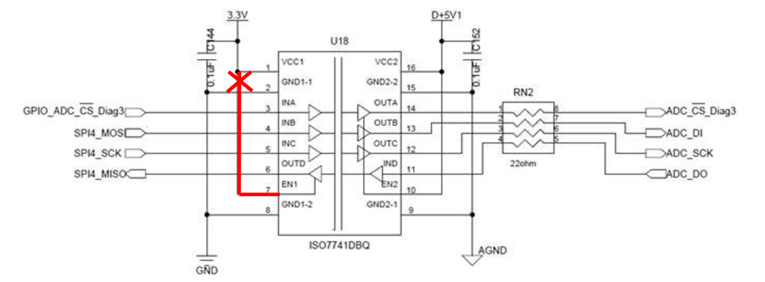

Iso7741 is used to isolate SPI data.

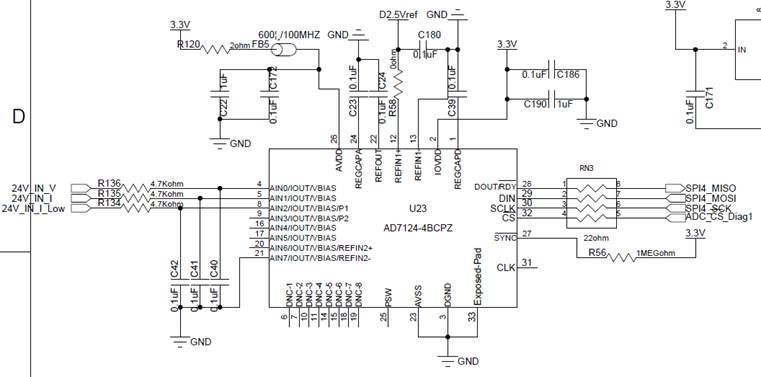

The left side of ISO7741 is a single-chip microcomputer and 1 ADC, and the right side of ISO7741 is 3 ADCs.

The single-chip microcomputer can only correctly read the data of the three ADCs on the right side, but the ADC data on the left side cannot be read. If iso7741 is removed, the ADC data on the left can be read correctly.

ADC-Analog Data Converter

Thanks

Elsa Duan