Other Parts Discussed in Thread: LMG1205, TLV3601, TLV3502, LMG1210

Hello TI experts,

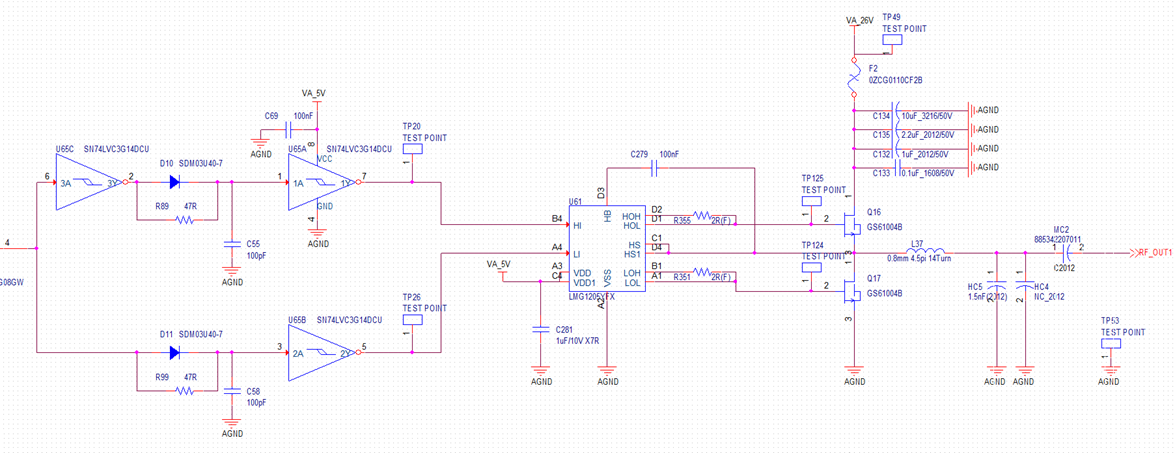

My customer considers to use SN74LVC3G14 and LMG1205 for their product, and I already got some advice for LMG1205 in previous post.

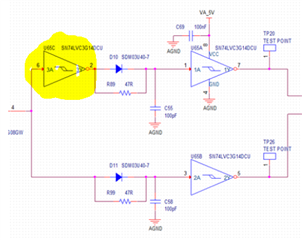

and now I want you to review the rest of the schematic.

you can see 2 resistors, R89 and R99 below.

my customer already tested that reducing the value of R89 and 99, the efficiency got little higher. (it worked as they expected)

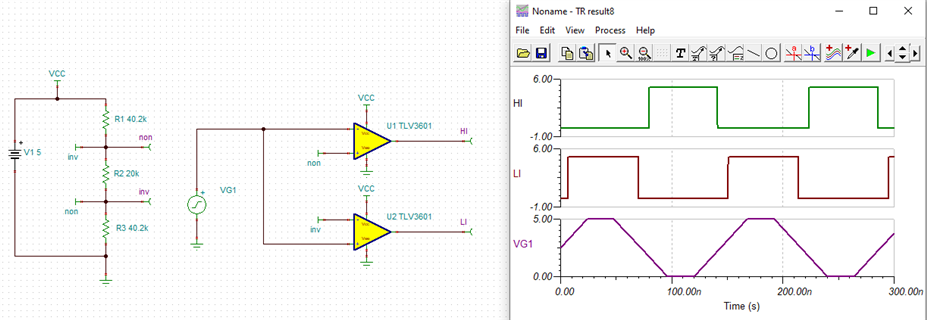

but as you know, if we reduce the value too much of R89 and R99, we may see the zero cross between 2 signals.

Do you have any idea about the minimum value of avoiding zero cross?

Please check this issue. Thanks.

Best regards,

Chase