Hi team,

I'm Ives Li, FAE in SZ AA1 team.

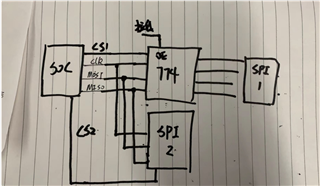

My customer TCL is using SN74AVC4T774 in their application as showed below:

And they found that the MISO input from SPI1 cannot be pulled down by SoC and SPI2, it will affect the SPI2 to work wrongly.

They try to use CS of SPI1 to control OE of 774 to solve this problem, could you help to verify if this solution could work?

More information:

- VCCA and VCCB is 3.3V, and when they try to output a low level for SOC's MISO, it can only be pull down to 2.5V but not 0V.

- Even they didn't connect the SPI1 device, the SoC still cannot pull low MISO.

Thanks!

Ives Li