Hi

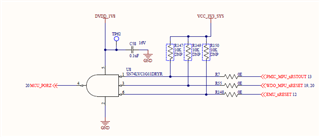

We have used SN74LVC1G11DRYR in our design based on AM625x. We have used this AND gate for our reset logic. Below is our implementation,

The issue we are facing is when the signal connected to pin 6(emu_reset which is a signal driven externally when connected to XDS110 debugger) is asserted low the output of the AND gate is not going low.

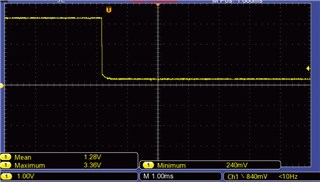

We have provided 4.7K pull up on the emu reset signal. Following is the waveform when we probed emu reset,

We tried giving various other pull up options also to bring the VIL lesser than 240mV , but still the AND gate is not recognising this low and the o/p is always high.

To chk the AND gate, We isolated the emu reset signal by removing the series resistor and pulled it low to see if o/p is going low. We observed o/p low as expected.

We want to know why when emu reset signal(3.3V signal) is connected to an AND gate (powered by 1.8V) is giving an issue? i,e logic low on emu reset is not driven as logic low at o/p of AND gate