Other Parts Discussed in Thread: SN74LVC1G125

Hi,

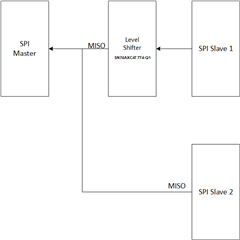

SPI devices configured in the device as shown below. MISO line is output from Level shifter.

When SPI slave-2 driving MISO line, working as expected.

When SPI slave-2 driving MISO line, MISO signal going upto 0.4V only(IO logic is 1.8V). SPI salve-2 can't drive MISO line to HIGH. Level shifter strongly driving the MISO line to "LOW".

When isolated Level shifter from the SPI bus, SPI slave-2 MISO line working as expected(1.8V level).

Does this expected behaviour when using SN74AXC4T774-Q1 ?