Part Number: TXB0108

Other Parts Discussed in Thread: TXV0108, TXS0108E

Hi Team,

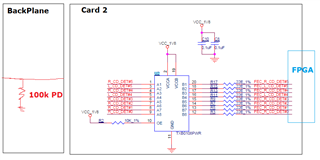

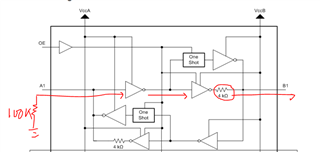

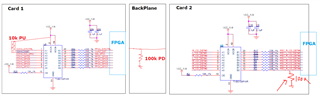

I am using TXB0108 between two cards connected in a backplane as a buffer. Below is my circuit. Both the TXBs are connected to FPGA, for card 1 it is configured as O/P, and for card 2 it is configured as I/P.

I have a PU of 10k on card 1 and a 100K PD in the backplane (connector card).

The purpose of the circuit is to sense/detect if card 1 is plugged (present) to the backplane or not.

I am facing an issue when the card is not plugged in the backplane, instead of reading 0 I am reading 1 from FPGA. When I checked with the multimeter I saw a logic high of 1.714V.

But because of the PD, it should read 0. I am clueless. Can anyone help me out with this.