Other Parts Discussed in Thread: SN74LVC1G123,

Tool/software:

Hi experts,

I want to know how to handle unused pins.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi experts,

I want to know how to handle unused pins.

Hi Clemens,

Thank you for suggesting another device. But since my customer plans to use SN74LV123A, we want to know what to do with this device.

Is there any other idea to solve this problem? Or, is there some information which I should ask customer?

By the way, the competition device (HD74LV123A) has the following description:

"The input pins for unused circuit should be used under conditions to fix the outputs to avoid malfunction cased by noises. Also, it's recommended that Rext / Cext terminals are open and external parts are not connected to."

https://www.renesas.com/jp/ja/document/dst/hd74lv123a-rej03d0314-0600z?language=en&r=527206

Hi Hiromu,

Luckily we have internal schematics for the design of these devices. I've taken a look and I think it's fine to leave these pins floating.

Best,

Malcolm

Hi Malcolm,

Thanks for the information. If possible, would you like to know why it's fine to leave these pins floating, do you have any information?

Best regards,

Hiromu

Hi Hiromu,

These signals are not connected to CMOS gates, they are connected to the drain, so there are not the same concerns in regard to oscillation or unknown voltage levels.

Best,

Malcolm

Hi Malcom,

Do you have any idea on why a abnormal heat issue happened by connecting the Rext and Cext pins to GND?

Regards

Ohashi

Ohashi,

It looks like this would allow for possible connection from VCC to GND under certain conditions. I am not a design engineer so I cannot answer confidently.

Best,

Malcolm

Hi Malcolm,

My customer wants to double check the internal circuit.

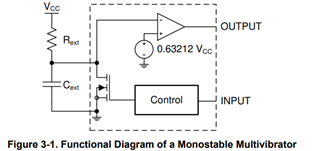

In this app note, seems that there is only low side FET for Rext and Cext.

https://www.ti.com/jp/lit/an/slva720a/slva720a.pdf

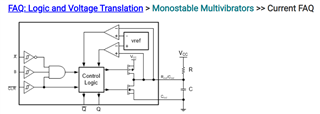

But in the below FQA, seems that there is high side p-FET between Vcc and Rexc/Cext. Seems that this FET was causing the heat issue in some kind of situation.

Which configuration is correct?

Regards

Ohashi

Hi Ohashi,

The second configuration is correct (with high side PFET).

Best,

Malcolm