Hello Team,

I'd like to ask you about SN74CB3T3245.

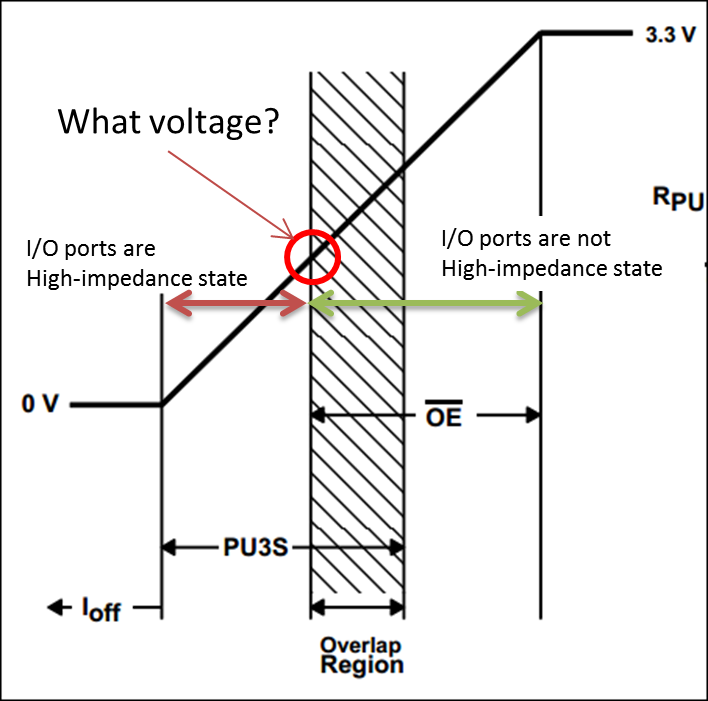

I understood that a high-impedance state exists between the A and B ports when /OE is High and Vcc=0V.

Is my understanding correct?

Also does a high-impedance state exist between the A and B ports when /OE is Low and Vcc=0 to 3.3V?

How many supply voltages is High-Z state of A and B ports canceled when /OE is Low and Vcc=0 to 3.3V if so?

Best Regards,

Hidetoshi Matsunami