Hi team,

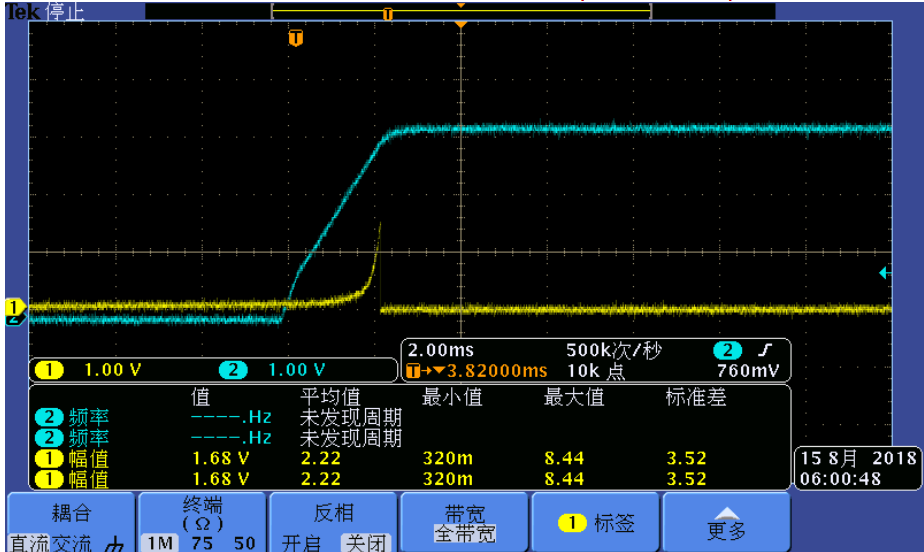

My customer find when they power up the SN74GTL1655, there is a spur occur when the supply voltage go to about 70% VCC.(see below)

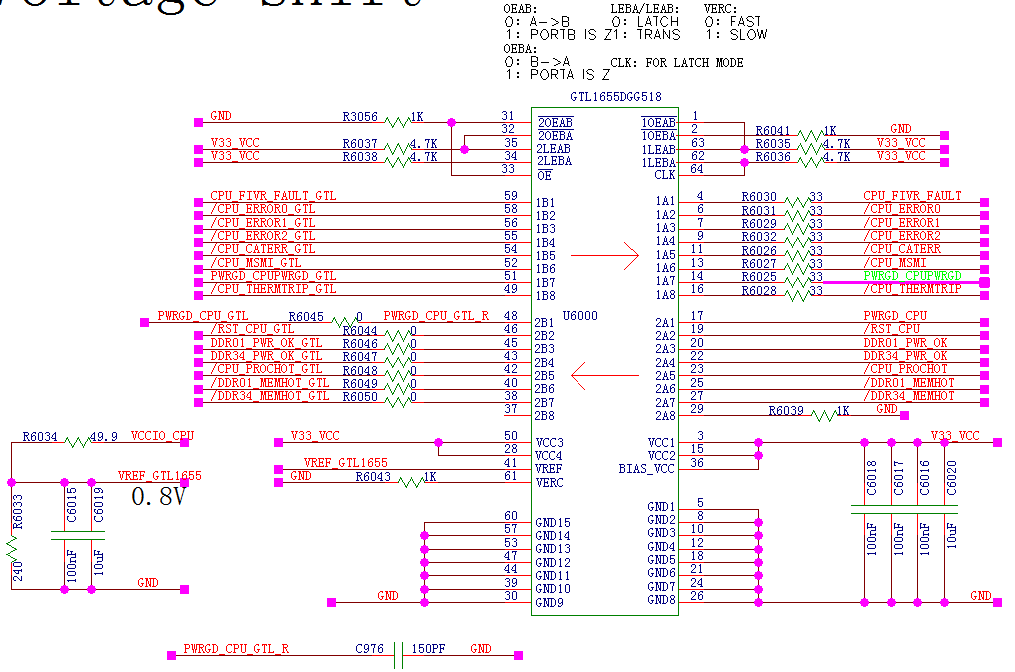

The blue on is the supply voltage, the yellow one is the output signal in 1A.(below is the schematic)

The rising time of the supply is about 2ms.

My customer connect the 1A to CPLD, and there is 4.7K pull up resistor and the input cap of the CPLD pin is about 5pf.

So for the spur, please help to answer below questions:

1. is it a normal performance of the part during the power up? If not, what may be the cause for the spur?

2. Can you help to analyze if there is method to eliminate the spur?

Lacey

Thanks a lot!