Dear all:

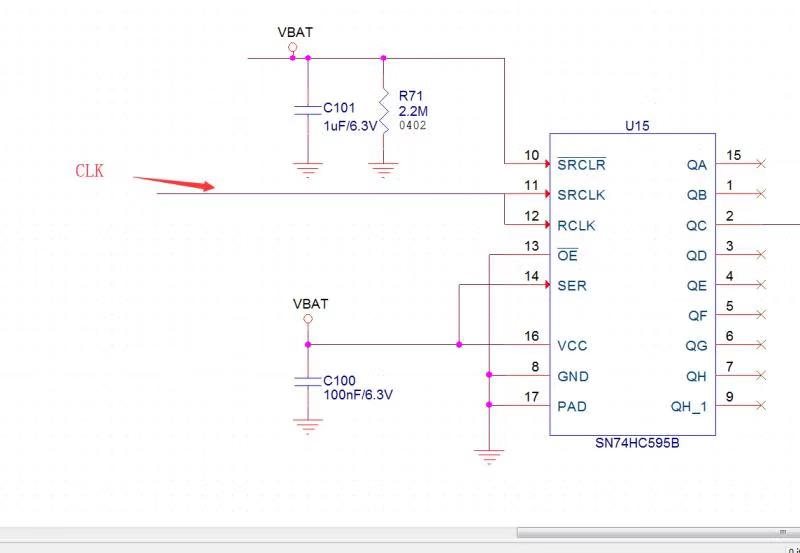

I use SRCLR=1,OE=0,SER=1,SRCLK is connected to RCLK

I want to achieve the function is to trigger a CLK high level, the output of the first high level;Then trigger a CLK high level, the output second high level;And so on

The circuit diagram is as follows:

But now I manually contact with VBAT for CLK, and then release.The output is all high. I connected the LED light at the output end, and the LED light is all bright.

Why is that? Can you give me some advice?

I use the domestic 595, with this circuit and this method test, the result is to trigger a high level, the output of a high, and so on