Hi Team,

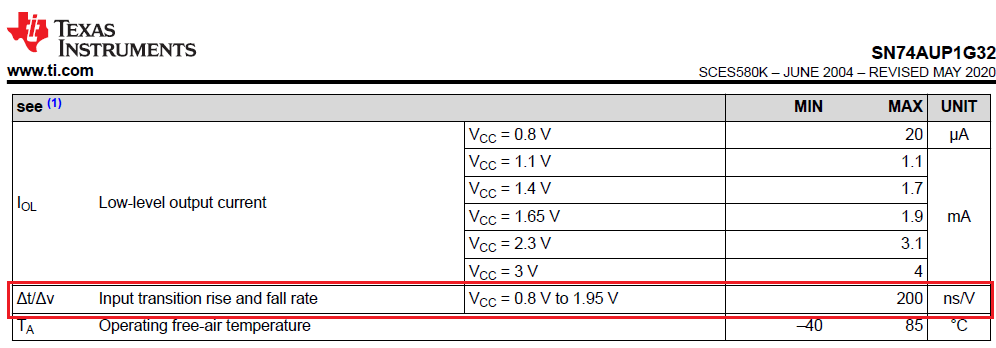

Our customer is confusing about the input transition rise and fall rate specification( Δt/Δv ) in the datasheet for SN74AUP1G32, as the usual understanding, the input voltage transition slew rate should be limited in V/us, but looks like we recommended the fast the better for this spec in datasheet with maximum 200ns/V. Can you help to clarify this spec? Does it mean 0 to 1V input voltage transient should be no more than 200ns?

Thanks.