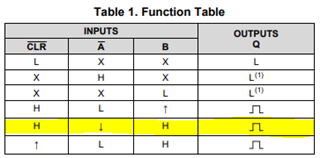

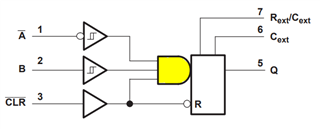

For input /A of this IC,we have to define the default state.In operation we provide 50Hz frequency to /A signal where B and /CLR signal is at high level. We have to do the pull-up or pull-down the signal at /A so that Output Q of this IC is at Low level.On other words we have to define the default state where Q should be at low level.

Could you please guide us when we pull up /A signal with B and /CLR signal at high level then what is the state at output Q? so basically to insure the output is at low level what should be the state of /A signal I have to set(low or high,need to supply from controller) where B and /CLR signals are at high level -pull ups are present on these two signals.