Hello,

I would like to use this device as Vcc=2.5V.

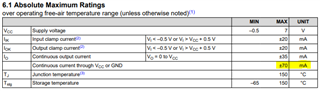

In this case, according to figure 6-1 and 6-2 of datasheet, it seems that high Ron resistance exist.

Therefore, I think that I need to consider Ioh and Iol from viewpoint of thermal.

Then, I found following document about Power consumption and thermal.

https://www.ti.com/lit/an/scaa035b/scaa035b.pdf?ts=1619498975965

https://www.ti.com/lit/an/scza005b/scza005b.pdf?ts=1619499015069

However, it seems that internal Ron resistance value is not applied on these document to calculate thermal.

Could you please tell me advice about how I should consider thermal information ?

Best Regards,