Other Parts Discussed in Thread: SN74LVC245A, SN74LVC244A,

Hello Andrea again writing,

just to inform you that issue is not yet resolved.

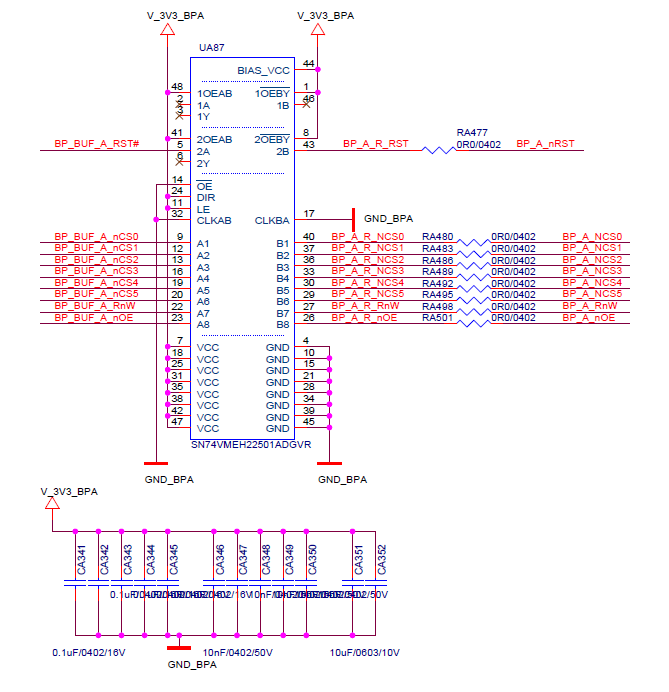

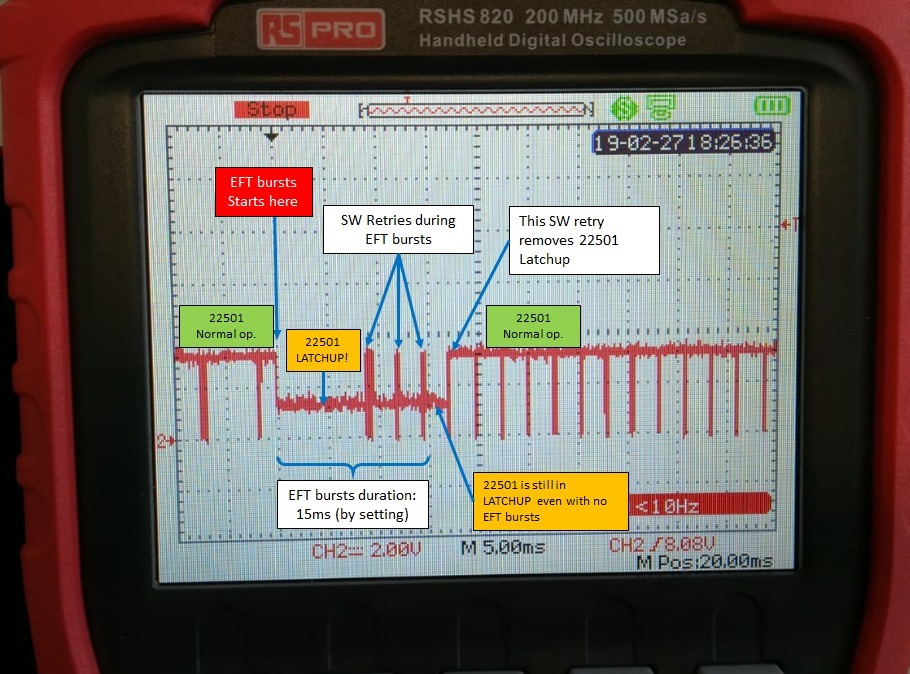

Given the circuit below, i move signals BP_BUF_A_nCSx from an FPGA. The output on the left side has issue when i apply a EFT burst

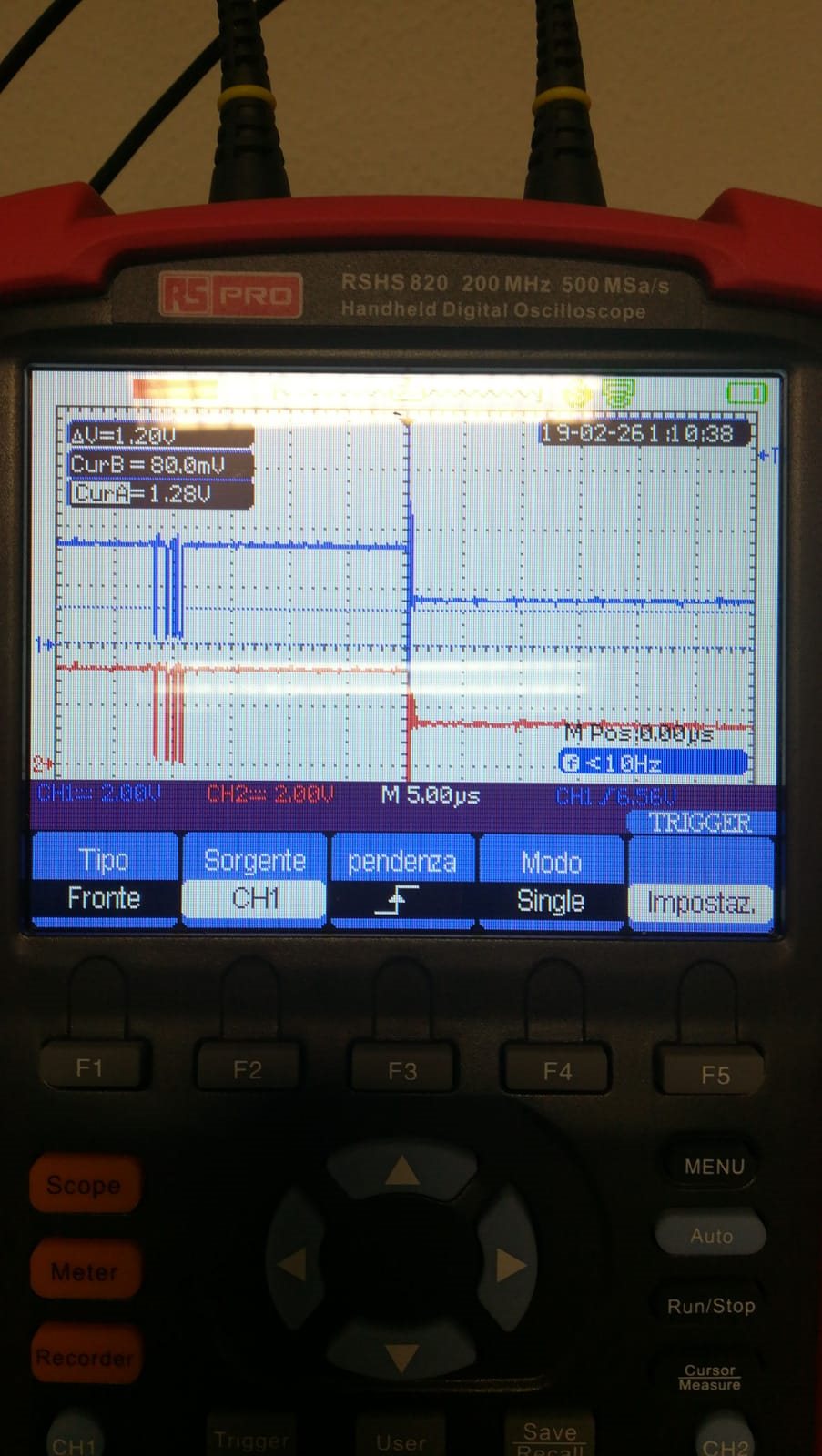

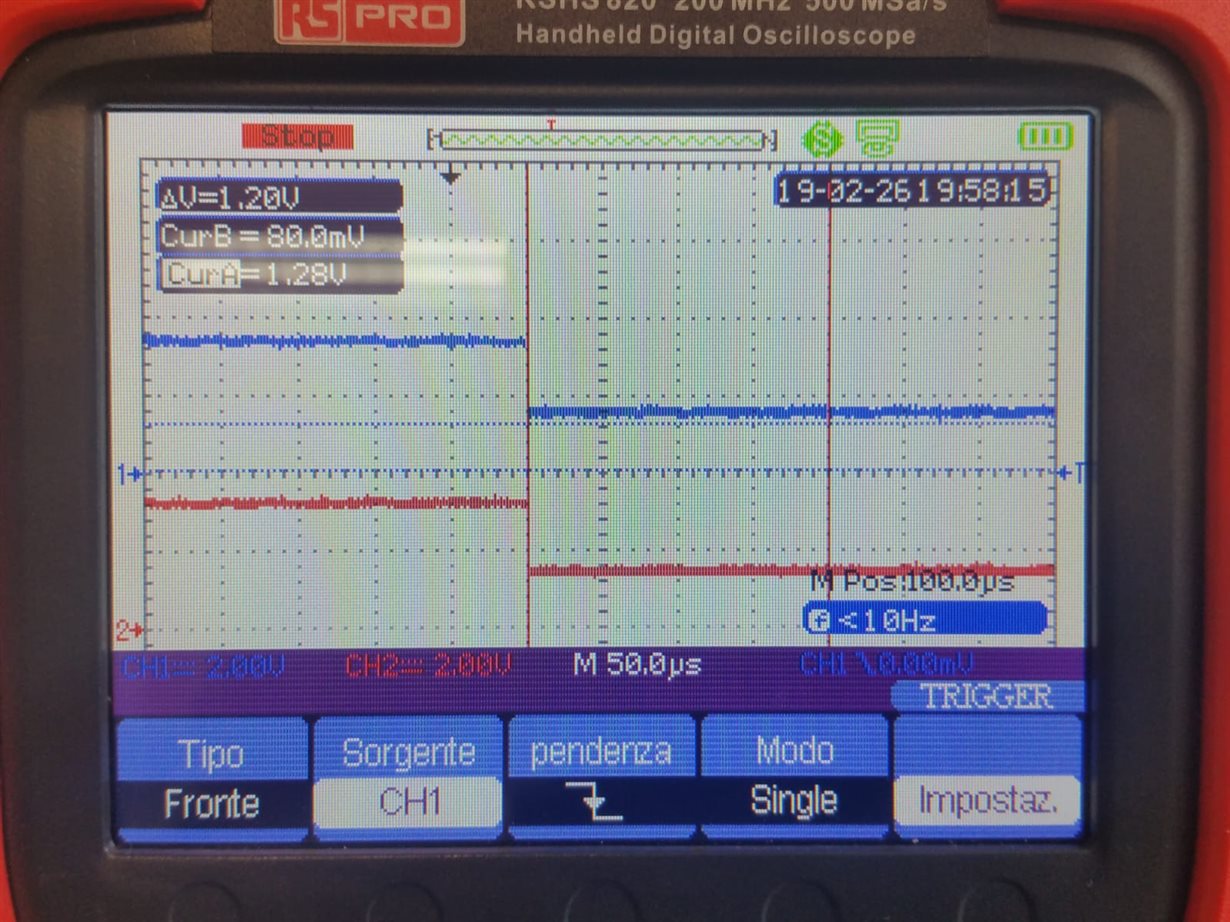

Find attached the waveform taken on the output signals *CS and *RnW: after the burst the signal is steady at 1.5V, instead of 3.3V.

Please an urgent feedback is required; possibly an italian field application engineer is appreciated.

Many thanks

Andrea