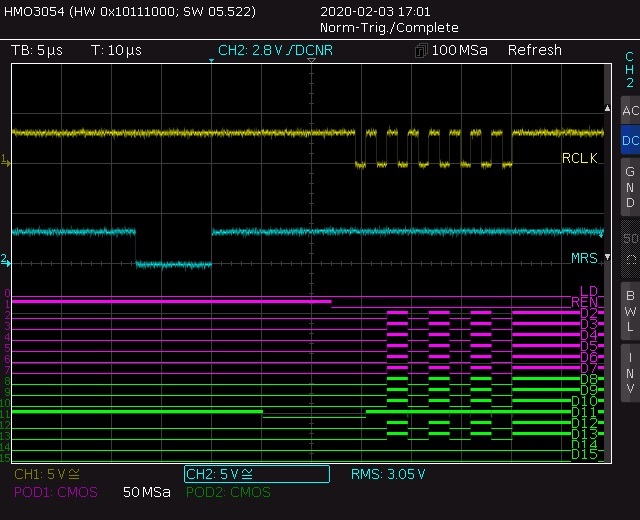

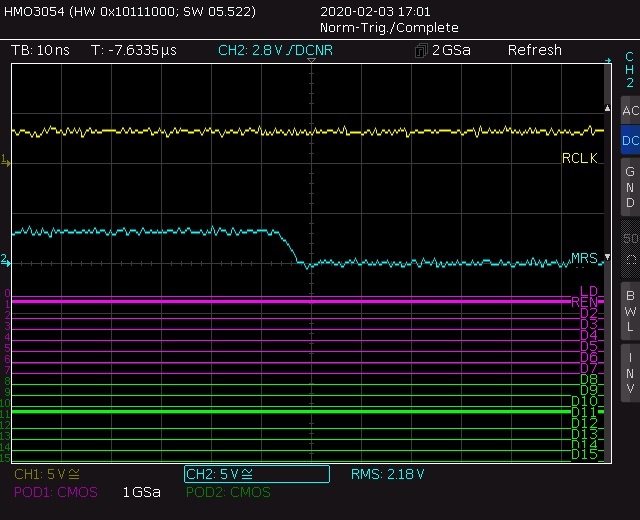

I have a number of prototype boards that incorporate 'V293 FIFOs. During configuration, firmware verifies the operation of components on the assembly, including the FIFOs.

The previous version of the prototype (using 'V293s with part marking 74COS9TG4) operates correctly, and returns the expected empty and full offset register values. In this application, both offset values are set to 16383 using pin straps.

The latest version of the prototype, populated with devices that have a part marking of 84AZVETG4, returns different values for the two offsets: the empty offset is incorrect (and its value varies from one run to another), but the full offset is always the correct value.

Are there any known issues with specific batches of these devices?