Other Parts Discussed in Thread: LSF0108, SN74LVC2G07, LSF0102, TINA-TI, SN74LVC1G07

Hello TI Logic Forum,

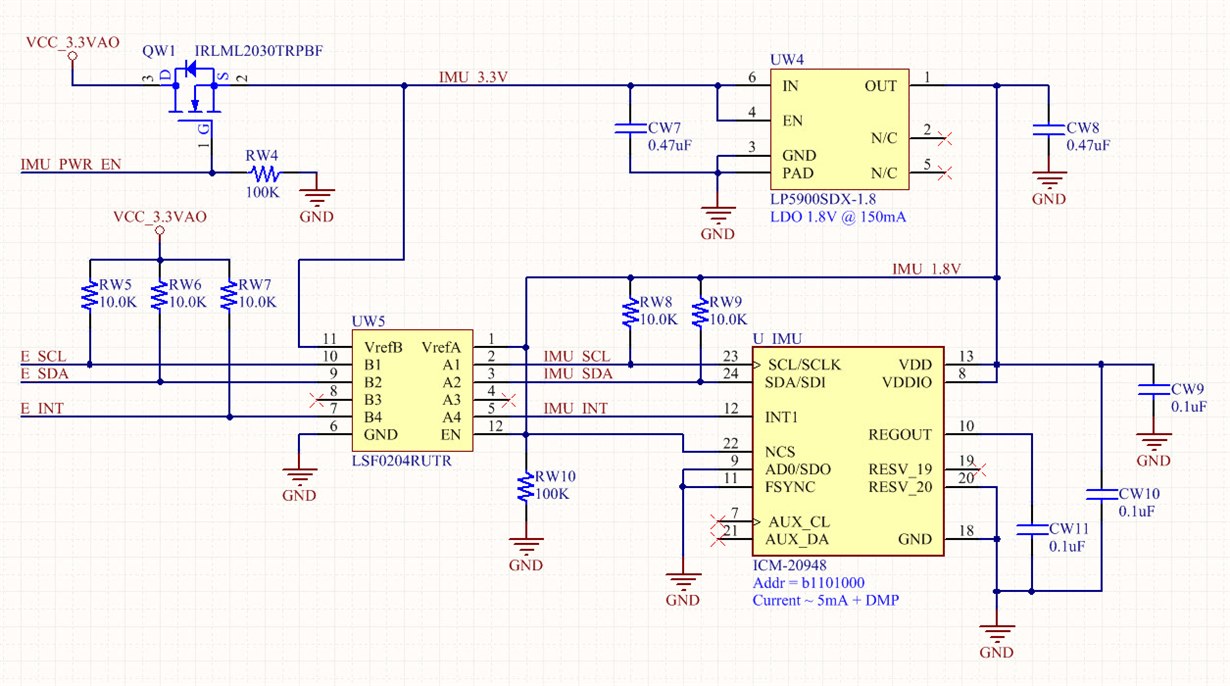

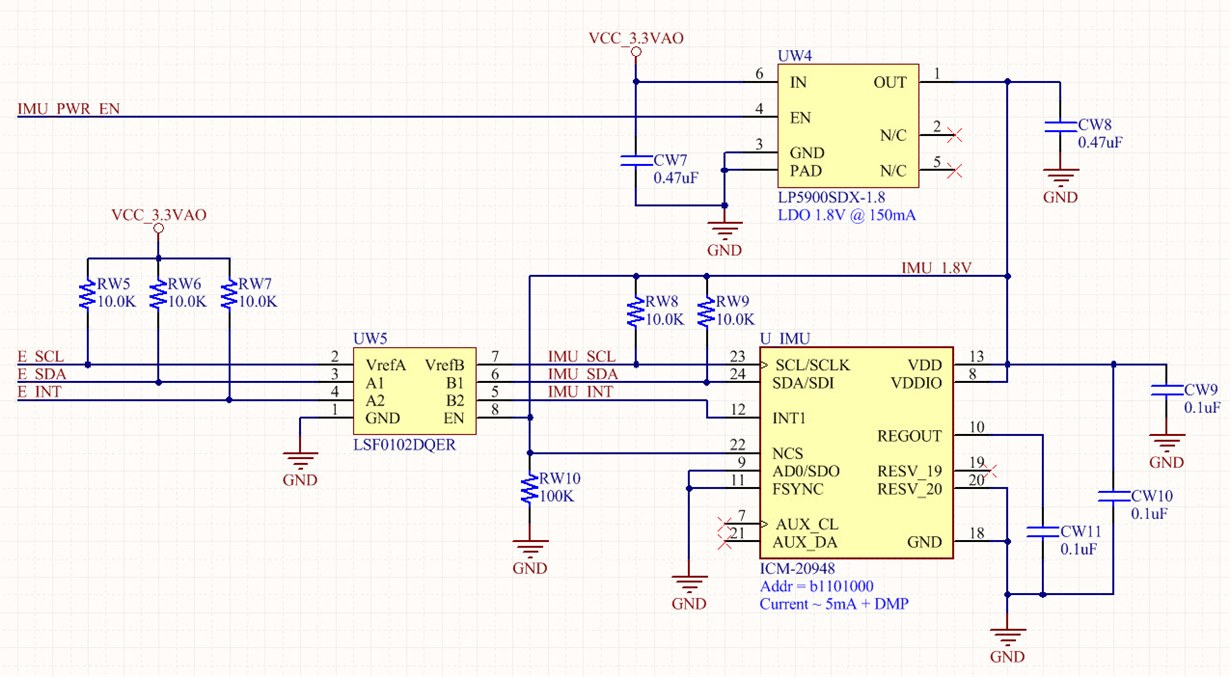

I need to translate an I2C bus and control signal between a 3.3V "Always On" processor and a 1.8V peripheral device that will often be powered off. Reading through other forum posts on the LSF0204, engineers reported significant parasitic power leakage between the A and B ports (with up to 1V appearing on the unpowered rail) due to the 200K internal resistor on Vref_B and general input leakage. That's highly undesirable for my design. I noticed that Ioff is only specified under the condition that Vref_A = Vref_B = 0 and not for a single unpowered port. So rather than simply disabling the 1.8V LDO and Vref_A of the LSF0204 with the IMU_PWR_EN signal, I'm proposing to also remove power from Vref_B using the NMOS FET at the top left of the schematic. Will that minimize the leakage and is there any downside to this approach that I'm overlooking?

Thanks,

Steve C