Other Parts Discussed in Thread: DCA1000EVM

The waveform of the raw data extracted by the cascade test demo in "mmwave_mcuplus_sdk_04_02_00_02" is abnormal. Please help analyze the reason for the abnormal data!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

The waveform of the raw data extracted by the cascade test demo in "mmwave_mcuplus_sdk_04_02_00_02" is abnormal. Please help analyze the reason for the abnormal data!

Hi,

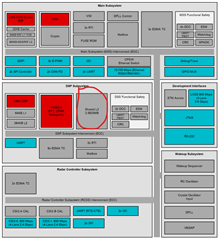

The radar platform we use is designed based on the dual cascade solution of AM273X provided by TI, and the DCA1000EVM was regarded as external capturing module, as well as the running program is the cascade test demo provided by TI.

Regards,

Yang

Hi Jitendra

Would you pls help provide some ideas what might be the reason for this abnormal ADC data issue? The amplitude of ADC data seem too high on these peaks.

Many Thanks

Ken

Hi Jitendra,

Some modifications were made by me to the test program for the 2cascade. Only the master AM2243 chip was turned on to scan, and just one chirp be launched in per frame. I turned off the "CASCADE_EVM" macro, and linked the non-cascaded libraries.

During the test, I found a strange phenomenon: as long as we do not power off the board, the abnormal amplitude data collected each time in multiple debugs are the same.

Regards,

Yang

Hi Jitendra,

Does L3RAM need some special initialization operation to use?

The reason why the question is asked is that during testing, we found that the noise in the result of performing the initialization operation would be much less than when the ping_pong_buffer was not initialized. The specific situation is as follows:

Therefore, I suspect that the ADC samples data was not written to SRAM successfully by the CSI bus. The data which be obtained from the ping_pong_buffer was actually gibberish generated by SRAM itself! The exact reason is unknown!

Regards,

Yang

Hi Jitendra,

After reviewing the datasheet of AM273X, I found that L3RAM is located in DSS! As only the MSS has been launched by our test program, the DSS was still in vacannt for it is not loaded! Is it because of this reason that L3RAM is in an unstable state, so the data written back through the CSI bus cannot be saved normally, so the data exported by CBUFF from L3RAM is actually a bunch of garbled characters! ! !

Regards,

Yang

Hi Jitendra,

It's my belief that the cause of the problem has been found, it should be the reason that the DSS is not powered on! The question now is how we launch the DSS via the programmatic API?

Regards,

Yang

Hi Jitendra

This thread is solved by powering DSP core and initilaizing L2 &L3 memory since the sample program is only running on ARM core.

The behavior difference between the HWs is still unknown.

Hi Ken, Libo,

Can you please let me know if something is to be answered in this thread?

Thanks and Regards,

Akshay.