- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

To my understanding, High-end ARM processors based on Cortex-A and Cortex-R include Performance Monitor Unit (PMU) which provides information like cycle counts.

Is there a way to activate this performance counter on the TI RM46?

Reference: ARM Cortex-R4 reference

Following this application note : https://www.ti.com/lit/fs/spna138a/spna138a.pdf?ts=1675176362803

I get the following

_pmuInit_(); _pmuEnableCountersGlobal_(); _pmuSetCountEvent_(pmuCOUNTER0, PMU_CYCLE_COUNT); // PMU_INST_ARCH_EXECUTED _pmuResetCounters_(); _pmuStartCounters_(pmuCOUNTER0); cycles_PMU_start = _pmuGetEventCount_(pmuCOUNTER0); code_to_be_measured(); _pmuStopCounters_(pmuCOUNTER0); cycles_PMU_end = _pmuGetEventCount_(pmuCOUNTER0); cycles_PMU_measure = cycles_PMU_end - cycles_PMU_start;

That said, it doesn't appear to work when I put this code in sys_main.c: the cycles_PMU_measure is still at 0.

Any help is appreciated.

Best,

Gabriel

Hi Gabriel,

Please use cycle counter to count the PMU cycles:

/*Reset Cycle Counter */

_pmuResetCounters_();

/*Start Cycle Counter */

_pmuStartCounters_(pmuCYCLE_COUNTER);

code_to_be_measured();

/*Stop Cycle Counter */

_pmuStopCounters_(pmuCYCLE_COUNTER);

/* read the CNNT cycle */

cycles= _pmuGetCycleCount_();Hi QJ,

You're right, this is working! I guess the app note I found was outdated.

My only problem is that in UserMode (CPRS M: 10000), calling the _pmuGetCycleCount_ makes my MCU crash.

I assume it's because the MRC instruction is touching P15 (is this the same thing as CP15 ?) and P15 must be somewhere protected by the MPU.

Do you know where P15 is located in memory, I'm not finding it in the reference manual.

I just noticed that your guide mentions _pmuEnableUserMode_();

This is exactly what I need! The only problem, it doesn't appear to exist in my HalCoGen-generated sys_pmu.h.

Do you have the assembly for this function?

Thanks for your help,

Gabriel

is this the same thing as CP15 ?

Yes, p15 in the MRC/MCR instructions stands for CP15 registers.

The PMU registers are always accessible in Privileged mode. You can use the User Enable (PMUSERENR) Register to make all of the PMU registers, except for the Interrupt Enable Set (PMINTENSET), and Interrupt Enable Clear (PMINTENCLR) Registers, accessible in User mode.

Do you know where P15 is located in memory, I'm not finding it in the reference manual.

It is not in ARM Cortex-R TRM: ARM DDI 0363C

https://developer.arm.com/documentation/ddi0363/g/Events-and-Performance-Monitor

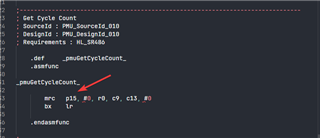

Do you have the assembly for this function?

You can download the example project from the link.

/* Enables User mode access to the PMU (must be called in a privileged mode)

***/

void _pmuEnableUserMode_(void)

{

asm(" MRC p15, #0, r0, c9, c14, #0"); //Read PMUSERENR Register

asm(" ORR r0, r0, #0x01"); //Set EN bit (bit 0)

asm(" MCR p15, #0, r0, c9, c14, #0"); //Write PMUSERENR Register

asm(" ISB"); //Synchronize context

}Hi QJ,

I have done some tests, and this solves my problem completely.

Thanks for your time.

Best regards,

Gabriel