Other Parts Discussed in Thread: SYSCONFIG

Hi Team,

I have custom AM2434_ALV processor connected with 4GB DDR4, pin configuration is same as AM2434 EVM board.

I have following question regarding DDR4

- I want to configure DDR with processor. Which settings i have to implement to get it done?

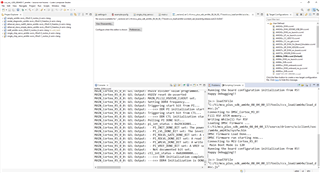

- I have tried with the default AM2434_EVM DDR script and its stuck in the attached image.

Please guide me.

--

Thanks & Regards,

Divyesh Patel