- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

I have custom AM2434_ALV processor connected with 4GB DDR4, pin configuration is same as AM2434 EVM board.

I have following question regarding DDR4

Please guide me.

--

Thanks & Regards,

Divyesh Patel

Hi Divyesh,

The DDR initialization in the gel file is for the DDR (8MB) used on the AM243x EVM. You may need to adjust it according to the size, timing etc. for the DDR used on your custom board. The file does the DDR initialization for AM243x EVM is at

C:\ti\ccs1200\ccs\ccs_base\emulation\gel\AM24x\AM24_DDRSS\AM24x_GP_EVM.gel

Best regards,

Ming

Hi Ming,

Thank you for your message.

Could you please provide me some procedures or references?

It will be very helpful for me.

—

Thanks & Regards,

Divyesh Patel

Hi Divyesh,

The DDR4 configuration tools and documentation are not in ideal situation. Here is what we have so far:

1. Go to SysConfig (ti.com) and add a new DDR4 instance

2. Use the generated AM243x-DDRConfig.gel to replace the C:\ti\ccs1200\ccs\ccs_base\emulation\gel\AM24x\AM24_DDRSS\AM24x-DDR4-1600MTs.gel

3. re-run the load_dmdsc.js and the AM2434_EVM DDR script.

You can also adjust the following:

1. DDR Memory Type

2. System Configuration

3. DRAM Timing A/B

4. IO Control A/B

Best regards,

Ming

Hi Ming,

Thank you for your guidance.

I am using ccs1110, does it work with it?

or need to go with ccs1200?

—

Thanks & Regards,

Divyesh Patel

Hi Ming,

I referred "https://software-dl.ti.com/mcu-plus-sdk/esd/AM243X/08_05_00_24/exports/docs/api_guide_am243x/DRIVERS_DDR_PAGE.html" for the DDR configuration.

Tried all 3 methods using

but i am not able to generate .gel file

How to generate .gel file? Please guide what wrong steps i have done.

--

Thanks & Regards,

Divyesh Patel

Hi Divyesh,

It should work for CCS 11.1 too. Please try the steps I suggested in previous post:

---------------------------

The DDR4 configuration tools and documentation are not in ideal situation. Here is what we have so far:

1. Go to https://dev.ti.com/sysconfig/?product=Processor_DDR_Config&device=AM243x_beta and add a new DDR4 instance:

2. Use the generated AM243x-DDRConfig.gel to replace the C:\ti\ccs1200\ccs\ccs_base\emulation\gel\AM24x\AM24_DDRSS\AM24x-DDR4-1600MTs.gel

3. re-run the load_dmdsc.js and the AM2434_EVM DDR script.

You can also adjust the following:

1. DDR Memory Type

2. System Configuration

3. DRAM Timing A/B

4. IO Control A/B

-----------------------------

Best regards,

Ming

Hi Ming,

I have created .gel file and replaced in the given link

Use the generated AM243x-DDRConfig.gel to replace the C:\ti\ccs1200\ccs\ccs_base\emulation\gel\AM24x\AM24_DDRSS\AM24x-DDR4-1600MTs.gel

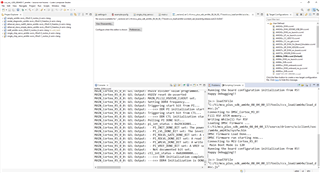

Then run script from Scripts->AM24 DDR Initialization -> AM24 DDR Initialization DDR Enabled/ Disabled both, but still stuck as per the attached image

and 2nd time its got failed as per the attached image

I have even tried with TMDS243GPEVM, with the default SDK configuration, still getting issue

Please guide me.

--

Thanks & Regards,

Divyesh Patel

Hi Divyesh,

The DDR4 configuration is very complicated, and it is highly dependent to the DDR4 you used.

Have you adjusted the DDR4 settings according to your DDR4 chip when you use https://dev.ti.com/sysconfig/?product=Processor_DDR_Config&device=AM243x_beta?

For AM243x GP EVM, you may try it with the latest MCU+ SDK 08.05.00.24 and CCS12.

Best regars,

Ming

Hi Ming,

Thank you for your response.

Have you adjusted the DDR4 settings according to your DDR4 chip when you use https://dev.ti.com/sysconfig/?product=Processor_DDR_Config&device=AM243x_beta?

Yes, I have done all configuration according to the my DDR4 chip.

I will try with CCS1200.

One more confusion is i have tried with EVM but in that also getting error

I have even tried with TMDS243GPEVM, with the default SDK configuration, still getting issue

why its so?

It should work with EVM bcz SDK is configured according to the EVM, then why it’s getting error

Please help me regarding this , it may give me some hint for my problem.

—

Thanks & Regards,

Divyesh Patel

Hi Divyeh,

I think it may be related to the target configuration file and the load_dmsc.js. I tried CS12.0.0 with MCU+ SDK 08.04.00.17 for AM64x using AM64x GP EVM instead of AM243 GP EVM as the default target configuration. It works properly with the following script:

loadJSFile "C:/ti/mcu_plus_sdk_am64x_08_04_00_17/tools/ccs_load/am64x/load_dmsc.js"

followed by the DDR initialization.

By the way the AM243x GP EVM an AM64x G EVM are the same physically.

Best regards,

Ming

Hi Ming,

I have successfully completed DDR initialization test, Write and Read test with AM2434 EVM.

But in my custom board, initialization & write test is done but unable to complete read test.

Please check my log and help me out.

DMSC_Cortex_M3_0: GEL Output: This GEL is currently only supported for use from the Cortex-M3 inside the DMSC. DMSC_Cortex_M3_0: GEL Output: Do not run this GEL from any other CPU on the SoC. DMSC_Cortex_M3_0: GEL Output: This script sets the first address translation region to [0x8000_0000, 0x0000_0000]. DMSC_Cortex_M3_0: GEL Output: It also sets the second address translation region to [0x6000_0000, 0x4000_0000]. DMSC_Cortex_M3_0: GEL Output: This is consistent with the SoC DV assumptions. DMSC_Cortex_M3_0: GEL Output: Configuring ATCM for the R5Fs DMSC_Cortex_M3_0: GEL Output: ATCM Configured. DMSC_Cortex_M3_0: GEL Output: R5F Halt bits set. DMSC_Cortex_M3_0: GEL Output: Configuring bootvectors DMSC_Cortex_M3_0: GEL Output: Bootvectors configured. DMSC_Cortex_M3_0: GEL Output: Programming all PLLs. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 0 (Main PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 0 (Main PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 1 (Peripheral 0 PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 1 (Peripheral 0 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 2 (Peripheral 1 PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 2 (Peripheral 1 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 8 (ARM0 PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 8 (ARM0 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 12 (DDR PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 12 (DDR PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 14 (Main Domain Pulsar) PLL) DMSC_Cortex_M3_0: GEL Output: Main PLL 14 (Main Domain Pulsar PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming MCU PLL 0 (MCU PLL) DMSC_Cortex_M3_0: GEL Output: MCU PLL 0 (MCU PLL) Set. DMSC_Cortex_M3_0: GEL Output: All PLLs programmed. DMSC_Cortex_M3_0: GEL Output: Powering up all PSC power domains in progress... DMSC_Cortex_M3_0: GEL Output: Powering up MAIN domain peripherals... DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_DMSC DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN_TEST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN_PBIST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMMC_4B DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMMC_8B DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_USB DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ADC DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_DEBUGSS DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_GPMC DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMIF_CFG DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMIF_DATA DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCAN_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCAN_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_SA2UL DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_SERDES_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PCIE_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_0_R5_0 DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_0_R5_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_PBIST_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_1. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_1_R5_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_1_R5_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_PBIST_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_1 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ICSSG_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_1. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ICSSG_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_1 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_CPSW. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_CPSW3G DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_CPSW done. DMSC_Cortex_M3_0: GEL Output: Powering up all MAIN domain peripherals done. DMSC_Cortex_M3_0: GEL Output: Powering up MCU Domain peripherals. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL_MCU. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_TEST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN2MCU DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCU2MAIN DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL_MCU done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_M4F. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_M4F DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_M4F done. DMSC_Cortex_M3_0: GEL Output: Powering up MCU Domain peripherals done. DMSC_Cortex_M3_0: GEL Output: Powering up all PSC power domains done! DMSC_Cortex_M3_0: GEL Output: DMSC_Cortex_M3_0: GEL Output: M4F WFI Vector set into IRAM. MAIN_Cortex_R5_0_0: GEL Output: Running from R5 MAIN_Cortex_R5_0_0: GEL Output: DDR not initialized with R5 connect. Go to menu Scripts --> AM64 DDR Initialization -> AM64_DDR_Initialization_ECC_Disabled to initialize DDR. ==== MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR4 Initialization is in progress ... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> ECC Disabled <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR controller programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR controller programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 0 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 0 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 1 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 1 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 0 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 2 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 1 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 1 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address slice 2 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 2 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> Set PHY registers for all FSPs simultaneously (multicast)... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Frequency not supported by GEL MAIN_Cortex_R5_0_0: GEL Output: Setting DDR4 frequency... MAIN_Cortex_R5_0_0: GEL Output: Triggering start bit from PI... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI initialization started... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Triggering start bit from CTL... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR CTL initialization started... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Polling PI DONE bit... MAIN_Cortex_R5_0_0: GEL Output: pi_int_status = 0x29C02001... MAIN_Cortex_R5_0_0: GEL Output: - PI_INIT_DONE_BIT set: The power-on initialization training in PI has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_LVL_DONE_BIT set: The leveling operation has completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_RDLVL_GATE_DONE_BIT set: A read leveling gate training operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_RDLVL_DONE_BIT set: A read leveling operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_WRLVL_DONE_BIT set: A write leveling operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_VREF_DONE_BIT set: A VREF setting operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - Not documented bit set. MAIN_Cortex_R5_0_0: GEL Output: ctl_int_status = 0x02000004... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR Initialization completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR4 Initialization is DONE! <<<--- MAIN_Cortex_R5_0_0: GEL Output: Starting Writes Test... MAIN_Cortex_R5_0_0: GEL Output: ...DDR Writes test Done! MAIN_Cortex_R5_0_0: GEL Output: Starting Reads Test: MAIN_Cortex_R5_0_0: Data verification failed at 0x80000000 Expected = 0x03020100 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: Data verification failed at 0x80000004 Expected = 0x04030201 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: GEL Output: DDR Reads test Done! MAIN_Cortex_R5_0_0: GEL Output: Starting WrRd Test 1: *wr32_ptr=i MAIN_Cortex_R5_0_0: Data verification failed at 0x80000000 Expected = 0x00000000 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: Data verification failed at 0x80000004 Expected = 0x01010101 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: GEL Output: Starting WrRd Test 2: *wr32_ptr=~i MAIN_Cortex_R5_0_0: Data verification failed at 0x80000000 Expected = 0x030100FF Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: Data verification failed at 0x80000004 Expected = 0x0100FFFE Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: GEL Output: !!!!! DDR Basic read/write test Failed !!!!

Which configuration can be wrong for this issue?

Please help me out.

--

Thanks & Regards,

Divyesh Patel

Hi Divyesh,

Can you share the spec of your DDR4 chip, the sysconfig settings and the gel file generated for your DDR4 chip?

Best regards,

Ming

Hi Ming,

I have 4GB DDR4 micron chip and its part number is MT40A256M16LY-062E:F TR, its datasheet is attached here.

micron_technology_mict_s_a0005091295_1-1764159.pdf

and also its sysconfig and gel

Please review and give me some suggestions.

--

Thanks & Regards,

Divyesh Patel

Hi Divyesh,

Thanks a lot for sending the part number and the data sheet. I will forward this to our DDR4 expert for further help. It may take some time.

Thank you very much for choosing TI device and appreciate your patience.

Hi Ming,

Thank you for your support.

I will wait for your feedback.

--

Thanks & Regards,

Divyesh Patel

Some of your latency parameters were incorrectly input into the tool. These need to be taken from the speed bin tables in the DDR datasheet for your operating speed. Try with: CL=14 and CWL = 9

REgards,

James

Hi James,

Thank you for your suggestion.

Try with: CL=14 and CWL = 9

I tried, but still same error. Is there any other parameters placed incorrectly?

--

Thanks & Regards,

Divyesh Patel

Something is wrong with your GEL. Line 137 shows "Frequency not supported by GEL"

In CCS, can you got to Help->About Code Composer Studio->Installation Details->Sitara Device Support. What is the version number? I think the latest is 1.6.3, see if you can update that package and retry.

If that doesn't help, please zip up the directory C:\ti\ccs1200\ccs\ccs_base\emulation\gel\am24x and post here, i will take a look.

Regards,

James

Hi James,

In CCS, can you got to Help->About Code Composer Studio->Installation Details->Sitara Device Support. What is the version number?

I have Sitara Device Support version v1.6.1. While updating it inform no updates, so i think it is the latest version.

I have attached am24x as well as am64x file.

Currently i am using am64x configuration, because earlier when i was trying with am24x then it was unable to initialize DDR and stuck in the "POLLING PI done bit"

Then run script from Scripts->AM24 DDR Initialization -> AM24 DDR Initialization DDR Enabled/ Disabled both, but still stuck as per the attached image

Please help me out.

--

Thanks & Regards,

Divyesh Patel

Hi Divyesh, it appears the update isn't working either! Let just completely replace all the GELs:

-rename C:\ti\ccs1200\ccs\ccs_base\emulation\gel\am64x to am64x_old

- unzip the attachment to the same directory so you get a fresh set of GELs for am64x

-you might need to regenerate your target configuration for your board

-perform the DDR init and write/read tests like you did previously (ensure that no javascripts run in the scripting console)

-send the console output if it is still not working

/cfs-file/__key/communityserver-discussions-components-files/908/0358.AM64x.zip

Regards,

James

Hi JJD,

I tried with above configuration, but still getting same error.

PFA console output.

DMSC_Cortex_M3_0: GEL Output: This GEL is currently only supported for use from the Cortex-M3 inside the DMSC. DMSC_Cortex_M3_0: GEL Output: Do not run this GEL from any other CPU on the SoC. DMSC_Cortex_M3_0: GEL Output: This script sets the first address translation region to [0x8000_0000, 0x0000_0000]. DMSC_Cortex_M3_0: GEL Output: It also sets the second address translation region to [0x6000_0000, 0x4000_0000]. DMSC_Cortex_M3_0: GEL Output: This is consistent with the SoC DV assumptions. DMSC_Cortex_M3_0: GEL Output: Configuring ATCM for the R5Fs DMSC_Cortex_M3_0: GEL Output: ATCM Configured. DMSC_Cortex_M3_0: GEL Output: R5F Halt bits set. DMSC_Cortex_M3_0: GEL Output: Configuring bootvectors DMSC_Cortex_M3_0: GEL Output: Bootvectors configured. DMSC_Cortex_M3_0: GEL Output: Debugging enabled DMSC_Cortex_M3_0: GEL Output: Programming all PLLs. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 0 (Main PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x000003FF DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x000003FF DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 10 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x00000000 DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x00000000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 3 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #1 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 9 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #1 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #2 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 24 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #2 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #3 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 14 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #3 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #4 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 7 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #4 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #5 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 4 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #5 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #6 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 3 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #6 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #7 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 3 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #7 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #8 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 7 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #8 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #9 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 2 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #9 programmed. DMSC_Cortex_M3_0: GEL Output: Selected Main Domain PLL Controller. DMSC_Cortex_M3_0: GEL Output: Cleared bit 0 in the PLL controller control register. DMSC_Cortex_M3_0: GEL Output: Cleared bit 5 in the PLL Controller control register. DMSC_Cortex_M3_0: GEL Output: PLL controller is now in bypass mode. DMSC_Cortex_M3_0: GEL Output: Set reset isolation to prevent a warm reset from killing the PLL controller. DMSC_Cortex_M3_0: GEL Output: Set PLLDIV1 (output_div1). DMSC_Cortex_M3_0: GEL Output: addr: 0x80410124 = 0x00008000 DMSC_Cortex_M3_0: GEL Output: Clear GOSET. DMSC_Cortex_M3_0: GEL Output: GOSTAT is clear. DMSC_Cortex_M3_0: GEL Output: Set PLLDIV1 (output_div1). DMSC_Cortex_M3_0: GEL Output: Set ALN1. DMSC_Cortex_M3_0: GEL Output: addr: 0x80410104 = 0x00000012 DMSC_Cortex_M3_0: GEL Output: Set OCSEL to 0x12, point C on the observation clock input tree inside the PLL Controller. DMSC_Cortex_M3_0: GEL Output: addr: 0x80410148 = 0x00000002 DMSC_Cortex_M3_0: GEL Output: Set the clock control register to enable the OBSCLK output (bit 1). DMSC_Cortex_M3_0: GEL Output: Set GOSET to 1. DMSC_Cortex_M3_0: GEL Output: GOSTAT is clear. DMSC_Cortex_M3_0: GEL Output: Enable PLL Controller (write to bit 0 in control register). DMSC_Cortex_M3_0: GEL Output: Set GOSET to 0. DMSC_Cortex_M3_0: GEL Output: PLLCTRL reset is cleared. PLLCTRL is free. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 0 (Main PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 1 (Peripheral 0 PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x0000007F DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x0000007F DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 7 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x00000001 DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x00001000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 9 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #1 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 11 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #1 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #2 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 4 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #2 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #3 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 9 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #3 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #4 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 79 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #4 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #5 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 5 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #5 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #6 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 15 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #6 programmed. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 1 (Peripheral 0 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 2 (Peripheral 1 PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x000003FF DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x000003FF DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 10 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x00000002 DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x00002000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 5 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #1 DMSC_Cortex_M3_0: GEL Output: i: 1, HSDIV value is -1, don't program this one DMSC_Cortex_M3_0: GEL Output: HSDIV clock output disabled. DMSC_Cortex_M3_0: GEL Output: HSDIV #1 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #2 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 8 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #2 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #3 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 5 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #3 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #4 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 17 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #4 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #5 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 7 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #5 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #6 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 7 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #6 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #7 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 17 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #7 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #8 DMSC_Cortex_M3_0: GEL Output: i: 8, HSDIV value is -1, don't program this one DMSC_Cortex_M3_0: GEL Output: HSDIV clock output disabled. DMSC_Cortex_M3_0: GEL Output: HSDIV #8 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #9 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 4 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #9 programmed. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 2 (Peripheral 1 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 8 (ARM0 PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x00000001 DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x00000001 DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 1 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x00000008 DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x00008000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 1 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 8 (ARM0 PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 12 (DDR PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x00000001 DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x00000001 DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 1 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x0000000C DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x0000C000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 3 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 12 (DDR PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 14 (Main Domain Pulsar) PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x00000003 DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x00000003 DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 2 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x00680000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x0000000E DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x0000E000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 2 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #1 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 2 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #1 programmed. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: Main PLL 14 (Main Domain Pulsar PLL) Set. DMSC_Cortex_M3_0: GEL Output: Programming MCU PLL 0 (MCU PLL) DMSC_Cortex_M3_0: GEL Output: Unlocked PLL MMRs. DMSC_Cortex_M3_0: GEL Output: Read configuration MMRs. DMSC_Cortex_M3_0: GEL Output: temp value (HSDIV_Presence) = 0x0000001F DMSC_Cortex_M3_0: GEL Output: HSDIV presence value = 0x0000001F DMSC_Cortex_M3_0: GEL Output: Number of hsidvs: 5 DMSC_Cortex_M3_0: GEL Output: Parsed PLL configuration information. DMSC_Cortex_M3_0: GEL Output: Note: deskew PLL programming isn't implemented yet DMSC_Cortex_M3_0: GEL Output: This is a fractional PLL, continuing on with normal programming. DMSC_Cortex_M3_0: GEL Output: For debugging: DMSC_Cortex_M3_0: GEL Output: Base address: 0x04040000 DMSC_Cortex_M3_0: GEL Output: PLL index: 0x00000000 DMSC_Cortex_M3_0: GEL Output: PLL index register base: 0x00000000 DMSC_Cortex_M3_0: GEL Output: Register: 0x00000020 DMSC_Cortex_M3_0: GEL Output: Clocking scheme: 1 DMSC_Cortex_M3_0: GEL Output: Set PLL to external bypass via Control MMR. DMSC_Cortex_M3_0: GEL Output: Disabled PLL DMSC_Cortex_M3_0: GEL Output: Enabled noise-cancelling DAC. DMSC_Cortex_M3_0: GEL Output: Enabled the Delta-Sigma modulator. DMSC_Cortex_M3_0: GEL Output: Programmed Reference clock pre-divider in output clock divider register. DMSC_Cortex_M3_0: GEL Output: Programmed the integer feedback divider value in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Fractional Divider Value is -1, don't set the fractional divider. DMSC_Cortex_M3_0: GEL Output: Programmed the fractional feedback divider in Freq Control 0 register. DMSC_Cortex_M3_0: GEL Output: Disabled the 4-phase clock generator (clk_4ph_en) in the control register. DMSC_Cortex_M3_0: GEL Output: Enabled the FOUT4PHASE clocks in the control register. DMSC_Cortex_M3_0: GEL Output: Set the first post-divider value (POSTDIV1) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Set the second post-divider value (POSTDIV2) in the output divider control register. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #0 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 5 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #0 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #1 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 24 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #1 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #2 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 24 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #2 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #3 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 11 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #3 programmed. DMSC_Cortex_M3_0: GEL Output: Programming HSDIV #4 DMSC_Cortex_M3_0: GEL Output: hsdiv_value: 11 DMSC_Cortex_M3_0: GEL Output: HSDIV reset asserted DMSC_Cortex_M3_0: GEL Output: HSDIV divider value programmed. DMSC_Cortex_M3_0: GEL Output: HSDIV clock output enabled. Reset automatically de-asserted. DMSC_Cortex_M3_0: GEL Output: HSDIV reset de-asserted DMSC_Cortex_M3_0: GEL Output: HSDIV #4 programmed. DMSC_Cortex_M3_0: GEL Output: Selected MCU Domain PLL Conntroller. DMSC_Cortex_M3_0: GEL Output: Cleared bit 0 in the PLL controller control register. DMSC_Cortex_M3_0: GEL Output: Cleared bit 5 in the PLL Controller control register. DMSC_Cortex_M3_0: GEL Output: PLL controller is now in bypass mode. DMSC_Cortex_M3_0: GEL Output: Set reset isolation to prevent a warm reset from killing the PLL controller. DMSC_Cortex_M3_0: GEL Output: Set PLLDIV1 (output_div1). DMSC_Cortex_M3_0: GEL Output: addr: 0x84020124 = 0x00008000 DMSC_Cortex_M3_0: GEL Output: Clear GOSET. DMSC_Cortex_M3_0: GEL Output: GOSTAT is clear. DMSC_Cortex_M3_0: GEL Output: Set PLLDIV1 (output_div1). DMSC_Cortex_M3_0: GEL Output: Set ALN1. DMSC_Cortex_M3_0: GEL Output: addr: 0x84020104 = 0x00000012 DMSC_Cortex_M3_0: GEL Output: Set OCSEL to 0x12, point C on the observation clock input tree inside the PLL Controller. DMSC_Cortex_M3_0: GEL Output: addr: 0x84020148 = 0x00000002 DMSC_Cortex_M3_0: GEL Output: Set the clock control register to enable the OBSCLK output (bit 1). DMSC_Cortex_M3_0: GEL Output: Set GOSET to 1. DMSC_Cortex_M3_0: GEL Output: GOSTAT is clear. DMSC_Cortex_M3_0: GEL Output: Enable PLL Controller (write to bit 0 in control register). DMSC_Cortex_M3_0: GEL Output: Set GOSET to 0. DMSC_Cortex_M3_0: GEL Output: PLLCTRL reset is cleared. PLLCTRL is free. DMSC_Cortex_M3_0: GEL Output: Set the enable bit in the control register. DMSC_Cortex_M3_0: GEL Output: PLL is locked. DMSC_Cortex_M3_0: GEL Output: External bypass is disabled '0'. PLL and HSDIV clocks are engaging the rest of the SoC. DMSC_Cortex_M3_0: GEL Output: MCU PLL 0 (MCU PLL) Set. DMSC_Cortex_M3_0: GEL Output: All PLLs programmed. DMSC_Cortex_M3_0: GEL Output: Powering up all PSC power domains in progress... DMSC_Cortex_M3_0: GEL Output: Powering up MAIN domain peripherals... DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_DMSC DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN_TEST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN_PBIST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMMC_4B DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMMC_8B DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_USB DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ADC DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_DEBUGSS DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_GPMC DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMIF_CFG DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMIF_DATA DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCAN_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCAN_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_SA2UL DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_SERDES_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PCIE_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_CLUSTER_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_A53_CLUSTER_0 DMSC_Cortex_M3_0: GEL Output: ERROR: module state NOT changed! DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_A53_CLUSTER_0_PBIST DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_CLUSTER_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_A53_0 DMSC_Cortex_M3_0: GEL Output: ERROR: module state NOT changed! DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_1. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_A53_1 DMSC_Cortex_M3_0: GEL Output: ERROR: module state NOT changed! DMSC_Cortex_M3_0: GEL Output: Powering up PD_A53_1 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_0_R5_0 DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_0_R5_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_PBIST_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_1. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_1_R5_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_1_R5_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_PBIST_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_1 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_0. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ICSSG_0 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_0 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_1. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ICSSG_1 DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_1 done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_CPSW. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_CPSW3G DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_CPSW done. DMSC_Cortex_M3_0: GEL Output: Powering up all MAIN domain peripherals done. DMSC_Cortex_M3_0: GEL Output: Powering up MCU Domain peripherals. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL_MCU. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_TEST DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN2MCU DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCU2MAIN DMSC_Cortex_M3_0: GEL Output: No change needed. DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL_MCU done. DMSC_Cortex_M3_0: GEL Output: Powering up PD_M4F. DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_M4F DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully. DMSC_Cortex_M3_0: GEL Output: Powering up PD_M4F done. DMSC_Cortex_M3_0: GEL Output: Powering up MCU Domain peripherals done. DMSC_Cortex_M3_0: GEL Output: Powering up all PSC power domains done! DMSC_Cortex_M3_0: GEL Output: DMSC_Cortex_M3_0: GEL Output: *****DDR is configured using R5 or A53 GELs DMSC_Cortex_M3_0: GEL Output: M4F WFI Vector set into IRAM. MAIN_Cortex_R5_0_0: GEL Output: Running from R5 MAIN_Cortex_R5_0_0: GEL Output: DDR not initialized with R5 connect. Go to menu Scripts --> AM64 DDR Initialization -> AM64_DDR_Initialization_ECC_Disabled to initialize DDR. ==== MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR4 Initialization is in progress ... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> ECC Enabled <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> After priming ECC memory, enable ECC_CK bit with hotmenu AM64 DDR Memory config --> Enable_TI_InlineECC_CK_During_Reads()<<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR controller programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR controller programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 0 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 0 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 1 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 1 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 0 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Data Slice 2 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 1 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 1 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address slice 2 programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY Address Slice 2 programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY programming in progress.. <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> Set PHY registers for all FSPs simultaneously (multicast)... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PHY programming completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Debugging enabled MAIN_Cortex_R5_0_0: GEL Output: Setting MAIN_PLL12_HSDIV0_CLKOUT_400MHz MAIN_Cortex_R5_0_0: GEL Output: hsdiv_value: 3 MAIN_Cortex_R5_0_0: GEL Output: HSDIV reset asserted MAIN_Cortex_R5_0_0: GEL Output: HSDIV divider value programmed. MAIN_Cortex_R5_0_0: GEL Output: HSDIV reset de-asserted MAIN_Cortex_R5_0_0: GEL Output: MAIN_PLL12_HSDIV0_CLKOUT set. MAIN_Cortex_R5_0_0: GEL Output: Setting DDR4 frequency... MAIN_Cortex_R5_0_0: GEL Output: Triggering start bit from PI... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR PI initialization started... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Triggering start bit from CTL... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR CTL initialization started... <<<--- MAIN_Cortex_R5_0_0: GEL Output: Polling PI DONE bit... MAIN_Cortex_R5_0_0: GEL Output: pi_int_status = 0x29C02001... MAIN_Cortex_R5_0_0: GEL Output: - PI_INIT_DONE_BIT set: The power-on initialization training in PI has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_LVL_DONE_BIT set: The leveling operation has completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_RDLVL_GATE_DONE_BIT set: A read leveling gate training operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_RDLVL_DONE_BIT set: A read leveling operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_WRLVL_DONE_BIT set: A write leveling operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - PI_VREF_DONE_BIT set: A VREF setting operation has been completed. MAIN_Cortex_R5_0_0: GEL Output: - Not documented bit set. MAIN_Cortex_R5_0_0: GEL Output: ctl_int_status = 0x02000004... MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR Initialization completed... <<<--- MAIN_Cortex_R5_0_0: GEL Output: --->>> DDR4 Initialization is DONE! <<<--- MAIN_Cortex_R5_0_0: GEL Output: Starting WrRd Test 1: *wr32_ptr=i MAIN_Cortex_R5_0_0: Data verification failed at 0x80000000 Expected = 0x00000000 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: Data verification failed at 0x80000004 Expected = 0x01010101 Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: GEL Output: Starting WrRd Test 2: *wr32_ptr=~i MAIN_Cortex_R5_0_0: Data verification failed at 0x80000000 Expected = 0x030100FF Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: Data verification failed at 0x80000004 Expected = 0x0100FFFE Actual= 0xFFFFFFFF MAIN_Cortex_R5_0_0: GEL Output: !!!!! DDR Basic read/write test Failed !!!!

and do i need to change board_ddrReginit.h file from the following path

C:\ti\mcu_plus_sdk_am243x_08_04_00_17\source\drivers\ddr\v0\soc\am64x_am243x

Because its mentioned, in the Readme file of sysconfig.

# AM64x\AM62x\AM243x\AM62Ax DDR Register Configuration (v9.05) ## Procedure: 1) Select Add button at the top and choose the DDR Memory Type. Fields will be populated with default values for AM64x\AM62x\AM243x\AM62Ax EVMs<br> 2) Modify parameters based on your DDR device. Hover mouse pointer over each parameter and choose the help icon (?) for more explanation<br> 3) The 'Generated Files' section on the right has output files for your software (uboot, RTOS, or GEL) that can be saved. A SysConfig configuration script can also be saved and then reloaded at a later time using File->Open in Sysconfg. ### GEL The resulting .gel file should be placed in the CCS installation for your device, for example ccs\ccs_base\emulation\gel\AM64x\AM64_DDRSS, and loaded using a GEL_LoadGEL instruction (see example in ccs\ccs_base\emulation\gel\AM64x\AM64_DDRSS\AM64x_GP_EVM.gel) ### CMM The resulting .cmm file should be placed in the Lautherbach installation for your device. ### Linux u-boot The resulting .dtsi file should be placed in arch/arm/dts, and the include statement in k3-am642-r5-<board>.dts (eg., k3-am642-r5-evm.dts for the GP EVM, or k3-am642-r5-sk.dts for the StarterKit) should reference the new .dtsi file. The DDR driver will properly set the DDR frequency and initialize the DDR controller using the information in this .dtsi file ### MCU+ SDK (RTOS) The resulting .h file should be placed in mcu_plus_sdk_<device>_<version>\source\drivers\ddr\v0\soc\am64x_am243x and included by using the SysConfig for SDK tool when building your code. Please refer to the SDK API Guide mcu_plus_sdk_<device>_<version>\docs\api_guide_am64x\DRIVERS_DDR_PAGE.html for more information ## Revision History v8.10: initial stable version. Changes from previous versions include: - added read/write DBI selection for LPDDR4/DDR4. Default to enable write DBI for LPDDR4, read DBI for DDR4 to improve power supply noise and improve overall signal integrity - changed default value of CA ODT to 60ohm for both LPDDR4 and DDR4 - updated RTOS output to fix #ifdef - periodic write DQ leveling disabled to improve realtime performance - disabled "always-on" mode of the input enables for data bytes for power optimization - disabled VREF controller for addr/cmd signals for power optimization<br> v8.40: provides improved operation at 1600MTs for both LPDDR4 and DDR4. Changes from previous version include: - changed default value CTRLUPD_AREF_HP_ENABLE=0 - changed default value LPI_WAKEUP_EN=0 - changed cal_clk divider and PVT calibration interval. This change provides significant stability improvements for LPDDR4 and DDR4 operation at 1600MTs - fixed TOSCO_F0 calculation for LPDDR4 v8.80: added support for AM62x release, added support for high temp operation, Other misc fixes to align with documentation: - CTL_165[11]=1 (LPI_WAKEUP_EN) only applicable for AM62x - CTL_321[23:8] = 0xFFFF (CS_MSK_1) corrected value when rank 1 disabled v9.04: -changed wrlvl_delay_early_threshold=0x100 to allow write leveling to complete successfully for wider array of layouts<br> -add cmm output<br> -LPDDR4: phy_rddqs_latency_adjust changed to 0 default recommendation (this value gets optimized during training)<br> -LPDDR4: optimized training loops to support 1 operating frequency<br> -LPDDR4/DDR4: optimized IO calibration configuration based on operating frequency<br> -LPDDR4/DDR4: optimized internal calibration clock based on operating frequency<br> -LPDDR4: changed default MR22 ODTE-CS=1<br> -LPDDR4: changed rx_ctle_cs default to No Boost<br> -AM62x dual rank support<br> -updated to use sysconfig v1.15<br> -public release for AM62A LPDDR4 support<br> v9.05: -cleaned up supported frequencies

Please help me out.

--

Thanks & Regards,

Divyesh Patel

Eventually, the board_ddrReginit.h will need to be changed, but this should not be used when you are initializing the board with the GELs. That's why i asked if and javascripts are being used. Ensure that you are not running any javascript files in the scripting console. Also ensure that no other boot media are booted from when powering the board. To ensure this, set your boot mode to No Boot Mode, or ensure that your boot media is erased or removed (as in SD card). Are you running any javascript or unintentionally booting from your boot media?

After a failure with the latest configuration, can you send a register dump by using the following GEL script: Scripts->AM64 DDRSS Debug->Memory Debug->AM64 DDRSS CTL PI PHY MemDump

Regards,

James

Hi James,

PFA load_dmsc.js which i am running for initialization.

To ensure this, set your boot mode to No Boot Mode, or ensure that your boot media is erased or removed (as in SD card).

It is set in the NO BOOT mode.

Waiting for your feedback.

--

Thanks & Regards,

Divyesh Patel

Hi James,

PFA updated console output.