Hello TI,

I have a 2 core variant AM2432B and would like to run the example of the SBL_OSPI provided in the mcu_plus_sdk_am243x_08_05_00_24.

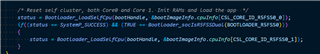

But, I am facing an error at the following line defined in main.c

"status = Bootloader_loadSelfCpu(bootHandle, &bootImageInfo.cpuInfo[CSL_CORE_ID_R5FSS0_1]);"

During debugging of the program, the value of the status is -1.

Can you please let me know, how to resolve this error?

Thanks & Regards

Teja