Hi,

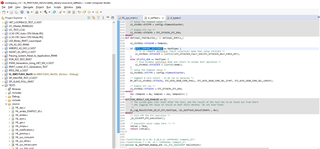

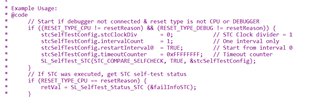

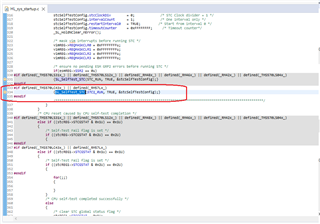

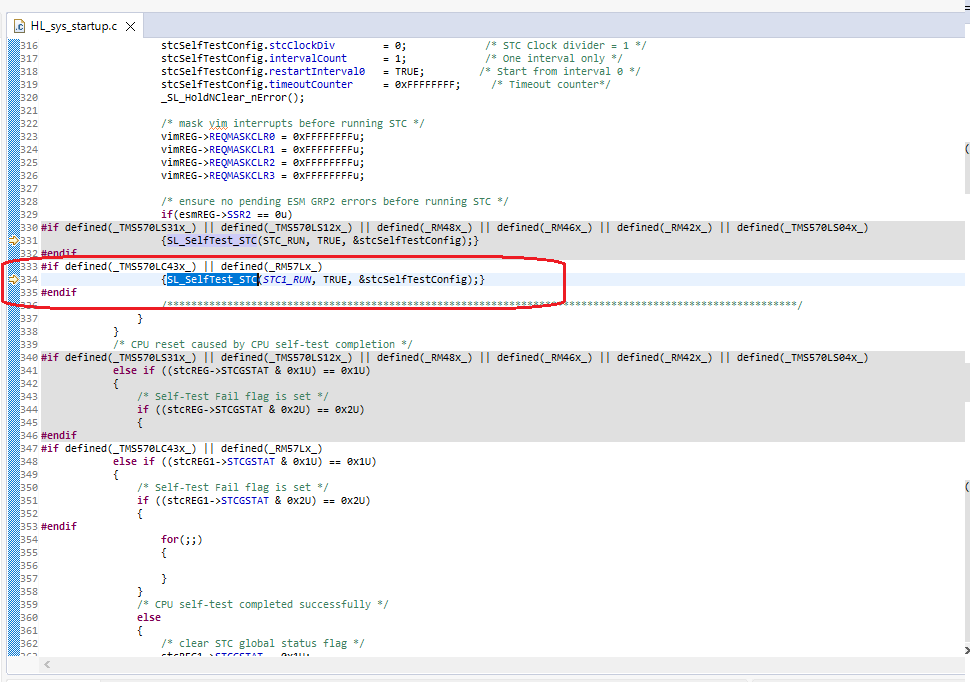

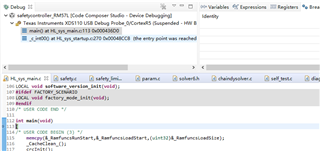

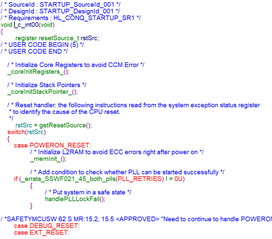

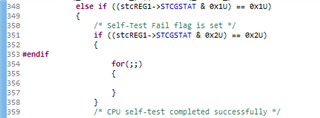

Now we need use SafeTI diagnostic library to executes CPU Logic Built-In Self Test using Self-Test Controller for RM57Lx MCU.

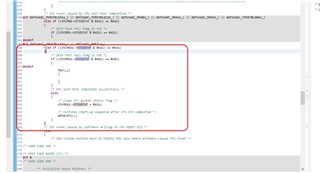

But I don't find related example code in Demo_app project, can you procide the example code for below test types with API SL_SelfTest_STC and SL_SelfTest_Status_STC?

Thanks so much!