Part Number: AM2434

Hi Team,

This is FAE Jayden, my customer o-net is evaluating AM2434 in their projects. Here is one question they raised. Could you help support?

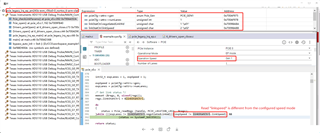

When PCIE was communicating normally in GEN2 mode, it was changed to the working mode of GEN1 (the working environment and code were the same, so only the working mode was changed), and it was found that it could not communicate normally. The debugging screenshot is as follows:

New Microsoft PowerPoint Presentation.pptx

New Microsoft PowerPoint Presentation.pptx

Brs

Jayden