Part Number: AM2434

Hi Experts,

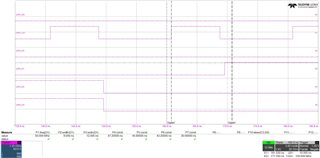

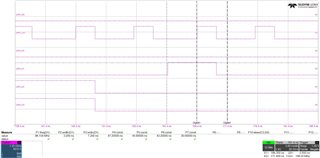

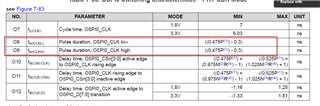

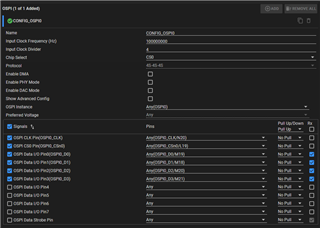

we have a QUAD SPI NOR Flash connected to the OSPI of the am243x and run it in QPI mode 4s-4s-4s. We noticed when recording with the oscillator that the high and low times of the clock do not match. In the manual of the flash 50% +-5% are allowed. I have made screenshots and attached them. One with 50MHz and one with 100MHz Clock. Can the high and low times be adjusted via register?