Other Parts Discussed in Thread: HALCOGEN, , TMS570LS1114, RM46L852, TMS570LS1224

Dear TI E2E design support staff,

i have a question about IOMM PINMMR registers configuration.

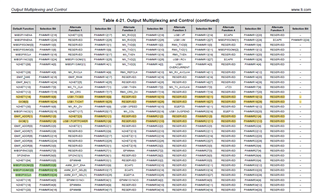

In particular, when using HalCoGen for QFP part, there appear some registers which are not referred in SPNU515C technical manual, table 4-21.

Following are statements from file pinmux.c used to configure PINMMR registers not mentioned in table 4-21:

pinMuxReg->PINMMR18 = PINMUX_PIN_125_HET1_14 | PINMUX_PIN_126_GIOB_0;

pinMuxReg->PINMMR21 = PINMUX_PIN_133_GIOB_1;

pinMuxReg->PINMMR24 = ((~(pinMuxReg->PINMMR20 >> 17U) & 0x00000001U ) << 16U) | ((~(pinMuxReg->PINMMR8 >> 9U) & 0x00000001U ) << 24U);

pinMuxReg->PINMMR25 = ((~(pinMuxReg->PINMMR12 >> 17U) & 0x00000001U ) << 8U) | ((~(pinMuxReg->PINMMR7 >> 9U) & 0x00000001U ) << 16U) | ((~(pinMuxReg->PINMMR0 >> 26U) & 0x00000001U ) << 24U);

pinMuxReg->PINMMR26 = ((~(pinMuxReg->PINMMR0 >> 18U) & 0x00000001U ) << 0U) | ((~(pinMuxReg->PINMMR9 >> 10U) & 0x00000001U ) << 8U);

pinMuxReg->PINMMR30 = 0x01010100U;

pinMuxReg->PINMMR32 = 0x00010101U;

Why do these registers have to be configured this way? Is there a technical manual to explain IOMM configuration with more detail?

Thanks for your attention and support,

best regards

Claudio Paglia