Other Parts Discussed in Thread: UNIFLASH,

Hi,

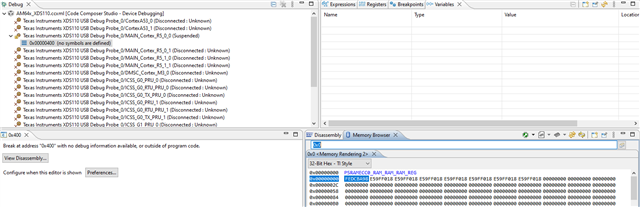

I'm using the am2432alv CPU with the mcu_sdk_243x.

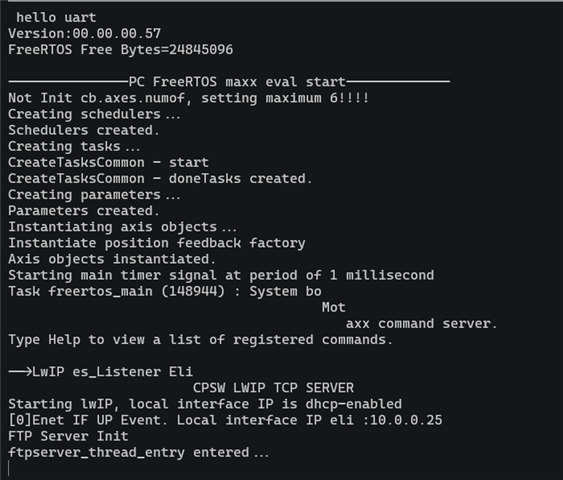

Usually, I load the code using the SDK loader via UART in UART-BOOT mode, then switch to OSPI-BOOT, and upon power-on, everything works fine.

Now, I've developed a FLASH device loader that loads binary files via FTP.

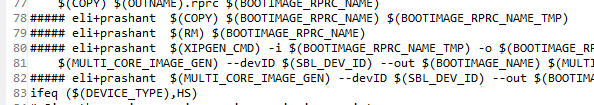

I've noticed the SDK SBL loader copies a binary file to the FLASH in UART-BOOT mode. However, I'm unsure whether it's the *.out or the *.rprc file that should be copied.

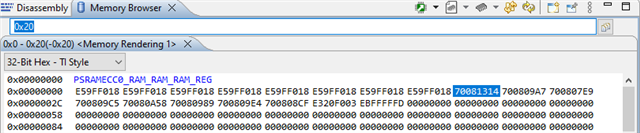

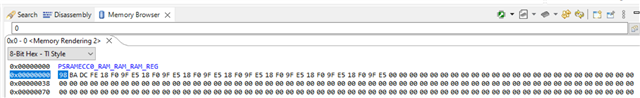

Additionally, I'm uncertain about the correct FLASH address - I assumed it was 0x80000, but I've observed 0x00080657 when reading from the FLASH.

Could you please advise?

Thanks,

Eli