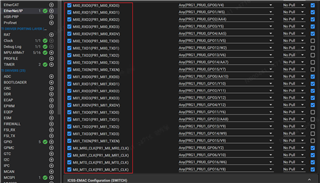

Other Parts Discussed in Thread: DP83869, DP83826E, SYSCONFIG

Hi experts,

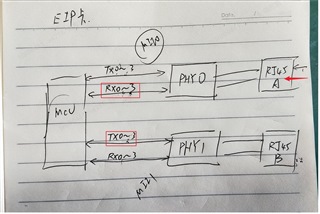

I am debugging my board which selects the chip AM2432 and DP83822 PHYs.

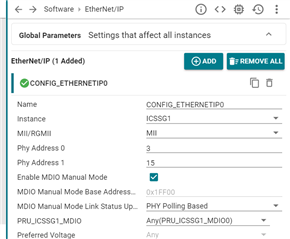

The eip stack in use is ind_comms_sdk_am243x_09_00_00_03 and I have not change the PHY driver code greatly.

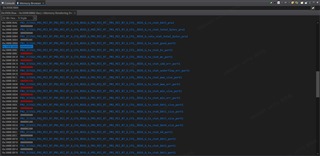

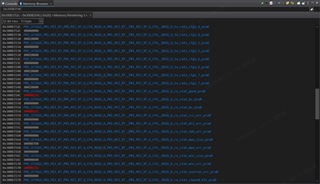

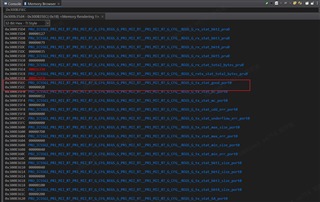

And this is the uart logs:

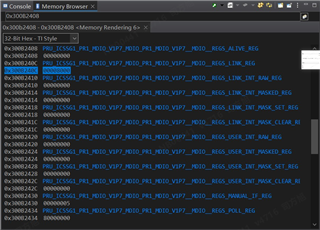

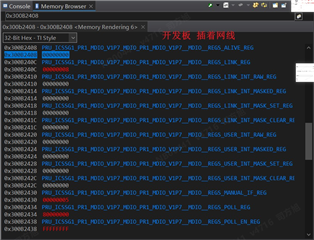

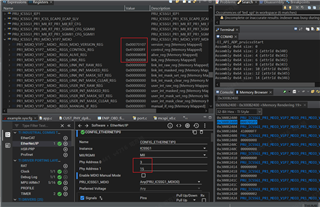

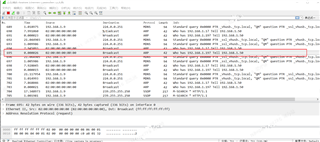

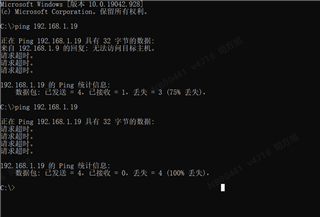

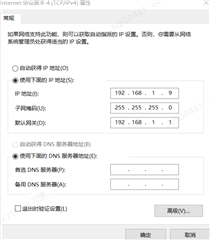

[MCSPI] Loopback example started 3 Pruicss max =3 selected PRU:3 The data is corrupted, write default values. Did Map 0x30080000 len 0x2000 to 0x30080000 (dram0) Did Map 0x30082000 len 0x2000 to 0x30082000 (dram1) Did Map 0x300b4000 len 0x4000 to 0x300b4000 (iram0) Did Map 0x300b8000 len 0x4000 to 0x300b8000 (iram1) Did Map 0x30090000 len 0x10000 to 0x30090000 (shdram) Did Map 0x300a2000 len 0x400 to 0x300a2000 (control0) Did Map 0x300a4000 len 0x400 to 0x300a4000 (control1) Did Map 0x300a0000 len 0x2000 to 0x300a0000 (intc) Did Map 0x300a6000 len 0x2000 to 0x300a6000 (cfg) Did Map 0x300a8000 len 0x2000 to 0x300a8000 (uart0) Did Map 0x300ae000 len 0x2000 to 0x300ae000 (iep) Did Map 0x300b0000 len 0x2000 to 0x300b0000 (ecap0) Did Map 0x300b2000 len 0x400 to 0x300b2000 (mii_rt) Did Map 0x3009f000 len 0x1c00 to 0x3009f000 (mdio) Did Map 0x3008a000 len 0x2000 to 0x3008a000 (txPru0Iram) Did Map 0x3008c000 len 0x2000 to 0x3008c000 (txPru1Iram) Did Map 0x300a5000 len 0x100 to 0x300a5000 (txPru0CtlReg) Did Map 0x300a5000 len 0x100 to 0x300a5000 (txPru1CtlReg) DP83822 detected DP83822 detected PRU_PHY_detect:185 Phy 1 alive PRU_PHY_detect:185 Phy 4 alive Phy 1 : REG[0x0000] = 0x3100 Phy 1 : REG[0x0001] = 0x7849 Phy 1 : REG[0x0002] = 0x2000 Phy 1 : REG[0x0003] = 0xA240 Phy 1 : REG[0x0004] = 0x01E1 Phy 1 : REG[0x0005] = 0x0000 Phy 1 : REG[0x0006] = 0x0004 Phy 1 : REG[0x0007] = 0x2001 Phy 1 : REG[0x0008] = 0x0000 Phy 1 : REG[0x0009] = 0x0000 Phy 1 : REG[0x000A] = 0x0100 Phy 1 : REG[0x000B] = 0x1000 Phy 1 : REG[0x000C] = 0x0000 Phy 1 : REG[0x000D] = 0x401F Phy 1 : REG[0x000E] = 0x0007 Phy 1 : REG[0x000F] = 0x0000 Phy 1 : REG[0x0010] = 0x4002 Phy 1 : REG[0x0011] = 0x0108 Phy 1 : REG[0x0012] = 0x0000 Phy 1 : REG[0x0013] = 0x0800 Phy 1 : REG[0x0014] = 0x0000 Phy 1 : REG[0x0015] = 0x0000 Phy 1 : REG[0x0016] = 0x0100 Phy 1 : REG[0x0017] = 0x0041 Phy 1 : REG[0x0018] = 0x0400 Phy 1 : REG[0x0019] = 0x8021 Phy 1 : REG[0x001A] = 0x0000 Phy 1 : REG[0x001B] = 0x007D Phy 1 : REG[0x001C] = 0x05EE Phy 1 : REG[0x001D] = 0x0000 Phy 1 : REG[0x001E] = 0x0102 Phy 4 : REG[0x0000] = 0x3100 Phy 4 : REG[0x0001] = 0x7849 Phy 4 : REG[0x0002] = 0x2000 Phy 4 : REG[0x0003] = 0xA240 Phy 4 : REG[0x0004] = 0x01E1 Phy 4 : REG[0x0005] = 0x0000 Phy 4 : REG[0x0006] = 0x0004 Phy 4 : REG[0x0007] = 0x2001 Phy 4 : REG[0x0008] = 0x0000 Phy 4 : REG[0x0009] = 0x0000 Phy 4 : REG[0x000A] = 0x0100 Phy 4 : REG[0x000B] = 0x1000 Phy 4 : REG[0x000C] = 0x0000 Phy 4 : REG[0x000D] = 0x401F Phy 4 : REG[0x000E] = 0x0007 Phy 4 : REG[0x000F] = 0x0000 Phy 4 : REG[0x0010] = 0x0002 Phy 4 : REG[0x0011] = 0x0108 Phy 4 : REG[0x0012] = 0x0000 Phy 4 : REG[0x0013] = 0x0800 Phy 4 : REG[0x0014] = 0x0000 Phy 4 : REG[0x0015] = 0x0000 Phy 4 : REG[0x0016] = 0x0100 Phy 4 : REG[0x0017] = 0x0041 Phy 4 : REG[0x0018] = 0x0400 Phy 4 : REG[0x0019] = 0x8024 Phy 4 : REG[0x001A] = 0x0000 Phy 4 : REG[0x001B] = 0x007D Phy 4 : REG[0x001C] = 0x05EE Phy 4 : REG[0x001D] = 0x0000 Phy 4 : REG[0x001E] = 0x0102 +EI_API_ADP_pruicssStart -EI_API_ADP_pruicssStart Assembly 0x64 size: 0 Assembly 0x64 size: 2 (attrId 0x340) Assembly 0x64 size: 4 (attrId 0x341) Assembly 0x64 size: 6 (attrId 0x342) Assembly 0x64 size: 8 (attrId 0x343) Assembly 0x64 size: 10 (attrId 0x344) Assembly 0x64 size: 12 (attrId 0x345) Assembly 0x64 size: 14 (attrId 0x346) Assembly 0x64 size: 16 (attrId 0x347) Assembly 0x64 size: 18 (attrId 0x348) Assembly 0x64 size: 20 (attrId 0x349) Assembly 0x64 size: 22 (attrId 0x34a) Assembly 0x64 size: 24 (attrId 0x34b) Assembly 0x64 size: 26 (attrId 0x34c) Assembly 0x64 size: 28 (attrId 0x34d) Assembly 0x64 size: 30 (attrId 0x34e) Assembly 0x64 size: 32 (attrId 0x34f) Local interface IP is 192.168.1.19 EI_API_ADP_getMacAddr: 1c:63:49:20:7c:bc

My question is how to make the two DP83822 PHYs work normally.

From the logs,can we find the problem takes place?What is the next step I should take?

Thank you.