Other Parts Discussed in Thread: SYSCONFIG, DP83822H

Tool/software:

Hi TI

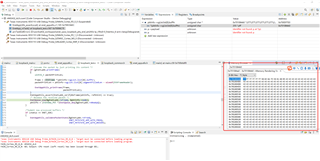

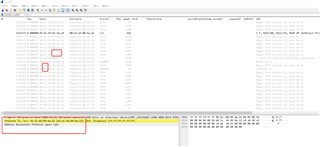

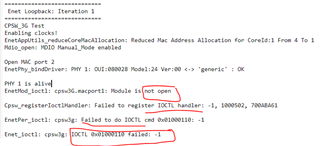

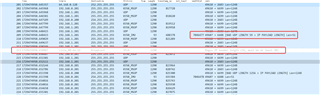

We are using am2432 with an external phy dp83822, when we power up our system, sometimes network failed.

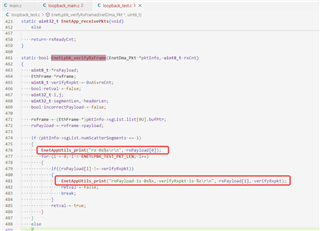

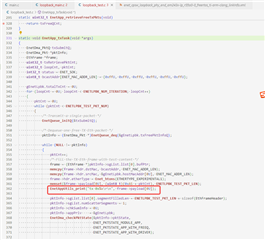

It seems that the content of the frame is changed and sometimes there is no frames at all. But local network connection is link up and unplug and reinsert the internet cable make no sense.

We develop our software based on demo "mcu_plus_sdk_am243x_09_02_01_05\examples\networking\lwip\enet_lwip_cpsw", how can we debug this issue, we don't know the issue is in cpsw or external phy.

We need your help. Thanks.