Tool/software:

Hi,

My customer wants to get better SYSOSC accuracy as much as possible.

They already enabled FCC with +/-0.1% 25ppm Rosc and got an expected result (0.53% at RT).

Is there any method to calibrate the value better?

According to TRM section 2.3.5, there is Frequency Clock Counter (FCC) and it can be used for calibration.

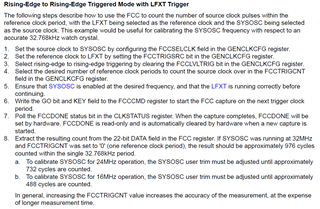

Below description in TRM section 2.3.5.1 shows how to use FCC with SYSOSC source and LFXT reference clock.

But it is not clear how to calibrate SYSOSC based on FCC count.

Thanks and regards,

Koichiro Tashiro