Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

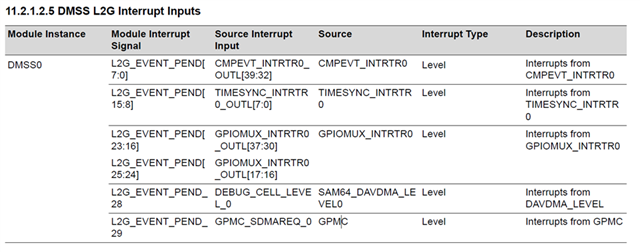

I'm using AM243x. I want to trigger a BCDMA channel transfer using a GPIO interrupt using L2G.

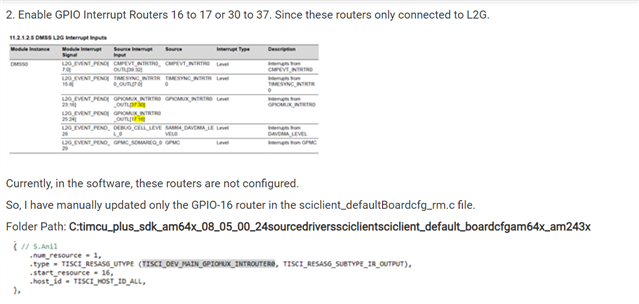

I have previously asked the question and got this answer:

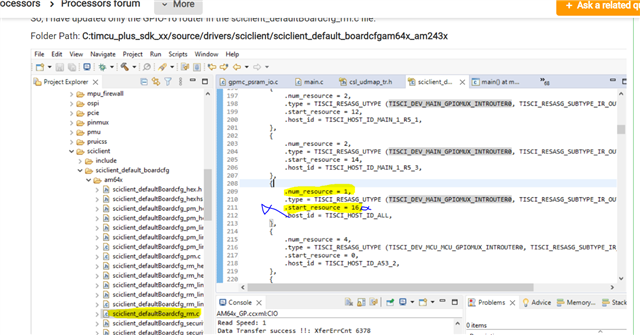

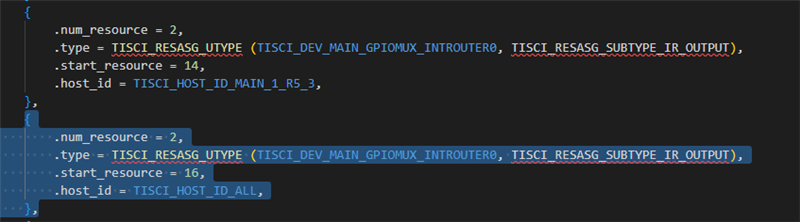

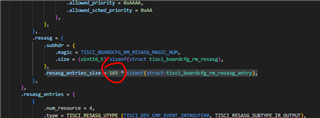

Now that I'm trying to configure it by sending the SCIclient message, it returns an unsuccessful. Previously I was told that since the GPIOMUX_out_16 is not routed, so I considered it can be the reason that it fails. I was told I should add it in the sciclient_defaultBoardcfg_rm.c as follows:

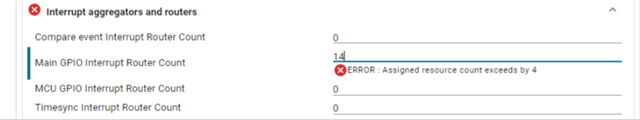

When I try to add it in boardcfg Sysconfig tool, it gives an error that it exceeds the number of resources as here:

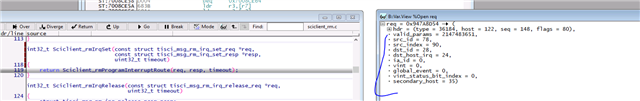

these are the configurations for the message that I'm sending to allocate a GPIO interrupt to trigger a bcdma_blkcpy channel. by mapping the interrupt to GPIOMUX_OUTP_16 mapped to L2G_24. the fields of the sciclient message to configure the interrupt is as in the second following picture.