Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

I am using AM2432 with the Industrial SDK 11.00.00.08.

We are doing some high temperature tests (around 90 degrees) with our custom sbl_ospi project on a custom board to see how our device behaves.

These are our results:

133 + NO PHY + NO DMA WORKS

133 + PHY + DMA WORKS

166 + NO PHY + NO DMA CRASH (first case)

166 + NO PHY + DMA CRASH (first case)

166 + PHY + DMA CRASH (second case)

We noticed two types of crashes.

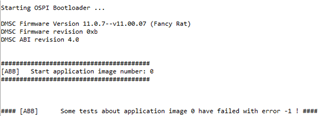

In the first case of crash it seems that the sbl ospi fails to authenticate the image, in particular it fails in: Bootloader_parseMultiCoreAppImage -> Bootloader_verifyMulticoreImage -> Bootloader_socAuthImage -> Sciclient_procBootAuthAndStart, where the check if((retVal != SystemP_SUCCESS) || ((respParam.flags & TISCI_MSG_FLAG_ACK) != TISCI_MSG_FLAG_ACK)) is true because of the respParam.flags part (while retVal == SystemP_SUCCESS).

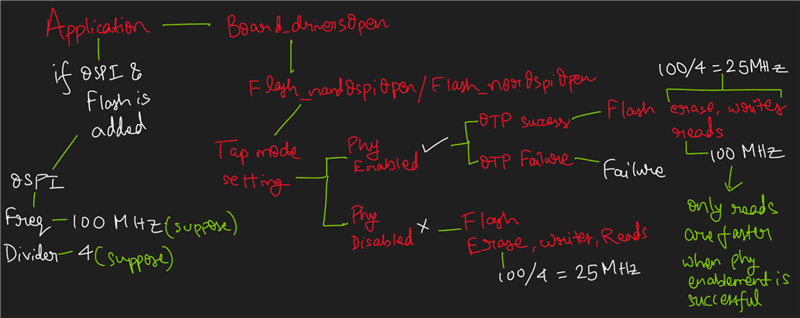

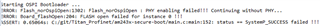

In the second case of crash instead the error seems more at the configuration level because sbl_ospi tries to enable PHY but fails:

The problems described happen at high temperatures, while at normal temperatures problems have never occurred.

We noticed that tests using 133 MHz frequency all seem to pass.

A strange behavior is that if the device is warmed up to high temperature but from off, then when turned on it sometimes does not give problems. The problems are there more often when the high-temperature module is left on for a while (about 1-2 minutes), then turned off and then turned on again. So it seems that somehow the module is sensitive to how long it has been on previously at the time of reboot.

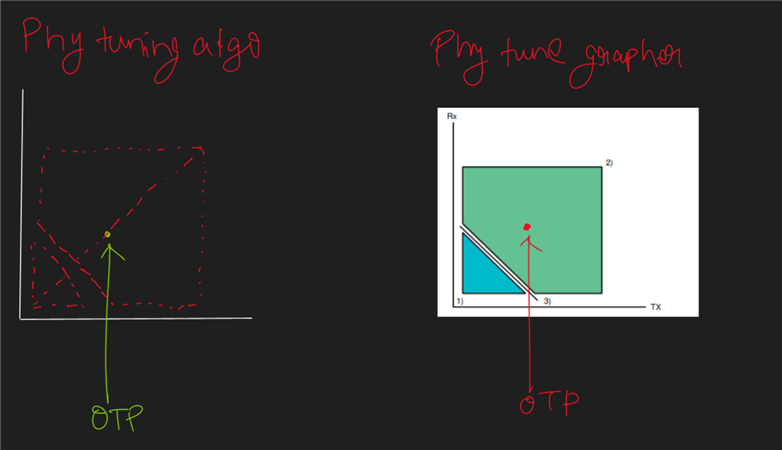

What can we do to better understand and solve the problem? Is this a problem already encountered? Does it have anything to do with the need for OSPI PHY tuning?

Thank you,

Kind Regards,

Andrea